Иерархия кэша, или многоуровневые кэши , относится к архитектуре памяти, которая использует иерархию хранилищ памяти, основанную на различных скоростях доступа к кэшируемым данным. Часто запрашиваемые данные кэшируются в хранилищах памяти с высокоскоростным доступом, что обеспечивает более быстрый доступ для ядер центрального процессора (ЦП).

Иерархия кэша - это форма и часть иерархии памяти, которую можно рассматривать как форму многоуровневого хранилища . [1] Эта конструкция была предназначена для того, чтобы ядра ЦП могли работать быстрее, несмотря на задержку доступа к основной памяти . Доступ к основной памяти может стать узким местом для производительности ядра ЦП, поскольку ЦП ожидает данных, в то время как обеспечение высокой скорости всей основной памяти может быть чрезмерно дорогостоящим. Высокоскоростные кэши - это компромисс, позволяющий получить высокоскоростной доступ к данным, наиболее часто используемым ЦП, что позволяет увеличить тактовую частоту ЦП . [2]

Фон [ править ]

В истории развития компьютеров и электронных микросхем был период, когда увеличение скорости процессора опережало улучшение скорости доступа к памяти. [3] Разрыв между скоростью ЦП и памятью означал, что ЦП часто простаивал. [4] ЦП становились все более способными запускать и выполнять большее количество инструкций за заданное время, но время, необходимое для доступа к данным из основной памяти, не позволяло программам в полной мере использовать эту возможность. [5] Эта проблема побудила к созданию моделей памяти с более высокой скоростью доступа, чтобы реализовать потенциал более быстрых процессоров. [6]

Это привело к концепции кэш-памяти , впервые предложенной Морисом Уилксом , британским ученым-компьютерщиком из Кембриджского университета в 1965 году. Он назвал такие модели памяти «подчиненной памятью». [7] Примерно между 1970 и 1990 годами статьи и статьи Ананта Агарвала , Алана Джея Смита , Марка Д. Хилла , Томаса Р. Пузака, и другие обсуждали более совершенные конструкции кэш-памяти. В то время были реализованы первые модели кэш-памяти, но даже когда исследователи изучали и предлагали более совершенные конструкции, потребность в более быстрых моделях памяти сохранялась. Эта потребность возникла из-за того, что, хотя ранние модели кеширования улучшали задержку доступа к данным, с точки зрения стоимости и технических ограничений кэш компьютерной системы не мог приблизиться к размеру основной памяти. Начиная с 1990 года, предлагались такие идеи, как добавление еще одного уровня кэша (второго уровня) в качестве резервной копии кеша первого уровня. Жан-Лу Баер, Вен-Ханн Ван, Эндрю Уилсон и другие провели исследования этой модели. Когда несколько симуляций и реализаций продемонстрировали преимущества двухуровневых моделей кэш-памяти, концепция многоуровневых кешей стала новой и в целом более совершенной моделью кэш-памяти. С 2000 года модели многоуровневого кэша получили широкое внимание и в настоящее время реализованы во многих системах, например, в трехуровневых кэшах, которые присутствуют в продуктах Intel Core i7. [8]

Многоуровневый кеш [ править ]

Доступ к основной памяти при выполнении каждой инструкции может привести к медленной обработке, так как тактовая частота зависит от времени, необходимого для поиска и выборки данных. Чтобы скрыть эту задержку памяти от процессора, используется кэширование данных. [9] Всякий раз, когда данные требуются процессору, они извлекаются из основной памяти и сохраняются в меньшей структуре памяти, называемой кешем. Если есть какие-либо дополнительные потребности в этих данных, сначала выполняется поиск в кэше, прежде чем переходить в основную память. [10] Эта структура находится ближе к процессору с точки зрения времени, затрачиваемого на поиск и выборку данных из основной памяти. [11]Преимущества использования кэша могут быть доказаны путем расчета среднего времени доступа (AAT) для иерархии памяти с кешем и без него. [12]

Среднее время доступа (AAT) [ править ]

Кеши, будучи небольшими по размеру, могут приводить к частым пропускам - когда поиск в кэше не дает искомой информации - что приводит к вызову основной памяти для выборки данных. Следовательно, на AAT влияет частота пропусков каждой структуры, в которой он ищет данные. [13]

AAT для основной памяти задается значением Hit time main memory . AAT для кешей может быть предоставлен

- Кэш времени попадания + ( кэш частоты промахов × время, затраченное на переход в основную память после пропуска кэша ). [ требуется дальнейшее объяснение ]

Время обращения к кешам меньше, чем время обращения к основной памяти, поэтому AAT для извлечения данных значительно ниже при доступе к данным через кеш, а не через основную память. [14]

Компромиссы [ править ]

Хотя использование кеша может улучшить задержку памяти, это не всегда может привести к требуемому улучшению времени, затрачиваемого на выборку данных, из-за способа организации и обхода кешей. Например, кэши с прямым отображением одинакового размера обычно имеют более высокий процент пропусков, чем полностью ассоциативные кэши. Это также может зависеть от теста компьютера, тестирующего процессор, и от набора инструкций. Но использование полностью ассоциативного кеша может привести к большему энергопотреблению, так как он должен каждый раз искать весь кеш. Из-за этого компромисс между потребляемой мощностью (и связанным с этим теплом) и размером кэша становится критическим при проектировании кэша. [13]

Эволюция [ править ]

В случае промаха кэша цель использования такой структуры станет бесполезной, и компьютеру придется обратиться к основной памяти, чтобы получить требуемые данные. Однако с многоуровневым кешем , если компьютер пропускает кэш, ближайший к процессору (кэш первого уровня или L1), он затем будет искать следующий ближайший уровень (уровни) кеша и перейдет в основную память, только если они методы терпят неудачу. Общая тенденция состоит в том, чтобы кэш L1 оставался небольшим и на расстоянии 1-2 тактовых циклов ЦП от процессора, при этом более низкие уровни кешей увеличивались в размере для хранения большего количества данных, чем L1, следовательно, они были более удаленными, но с меньшим количеством промахов. показатель. Это приводит к лучшему AAT. [15]Количество уровней кэша может быть спроектировано архитекторами в соответствии с их требованиями после проверки компромиссов между стоимостью, AAT и размером. [16] [17]

Увеличение производительности [ править ]

Благодаря масштабированию технологий, которое позволило разместить системы памяти на одном кристалле, большинство современных процессоров имеют до трех или четырех уровней кэш-памяти. [18] Уменьшение AAT можно понять на этом примере, где компьютер проверяет AAT на наличие различных конфигураций вплоть до кэшей L3.

Пример : основная память = 50 нс , L1 = 1 нс с частотой промахов 10%, L2 = 5 нс с частотой промахов 1%), L3 = 10 нс с частотой промахов 0,2%.

- Без кеша, AAT = 50 нс

- Кэш L1, AAT = 1 нс + (0,1 × 50 нс) = 6 нс

- L1–2 кэша, AAT = 1 нс + (0,1 × [5 нс + (0,01 × 50 нс)]) = 1,55 нс

- Кэши L1–3, AAT = 1 нс + (0,1 × [5 нс + (0,01 × [10 нс + (0,002 × 50 нс)])]) = 1,5 · 101 нс

Недостатки [ править ]

- Кэш-память имеет повышенную предельную стоимость, чем основная память, и, таким образом, может увеличить стоимость всей системы. [19]

- Кэшированные данные хранятся только до тех пор, пока кеш-память подается на питание.

- Увеличенная площадь на кристалле, необходимая для системы памяти. [20]

- Преимущества могут быть минимизированы или устранены в случае больших программ с плохой временной локальностью , которые часто обращаются к основной памяти. [21]

Свойства [ править ]

Банковские или унифицированные [ править ]

В банковском кэше кэш делится на кэш, выделенный для хранения инструкций, и кэш, выделенный для данных. Напротив, унифицированный кеш содержит как инструкции, так и данные в одном и том же кеше. [22] Во время процесса процессор обращается к кэшу L1 (или кэшу самого верхнего уровня в зависимости от его соединения с процессором) для извлечения как инструкций, так и данных. Требование одновременной реализации обоих действий требует нескольких портов и большего времени доступа в едином кэше. Наличие нескольких портов требует дополнительного оборудования и проводки, что приводит к значительной структуре между кэшами и процессорами. [23]Чтобы избежать этого, кэш L1 часто организован в виде банковского кэша, что приводит к меньшему количеству портов, меньшему количеству оборудования и, как правило, меньшему времени доступа. [13]

Современные процессоры имеют разделенные кеши, а в системах с многоуровневыми кешами кеши более высокого уровня могут быть объединены, а более низкие уровни разделены. [24]

Политика включения [ править ]

То, может ли блок, присутствующий в верхнем уровне кэша, также присутствовать на нижнем уровне кэша, регулируется политикой включения системы памяти, которая может быть включающей, исключающей или неисключающей, неисключительной (ДЕВЯТЬ). [25]

При использовании инклюзивной политики все блоки, присутствующие в кэше верхнего уровня, также должны присутствовать в кэше нижнего уровня. Каждый компонент кэша верхнего уровня является подмножеством компонента кэша нижнего уровня. В этом случае из-за дублирования блоков происходит некоторая потеря памяти. Однако проверка происходит быстрее. [25]

Согласно эксклюзивной политике, все компоненты иерархии кэша являются полностью исключительными, так что любой элемент в кэше верхнего уровня не будет присутствовать ни в одном из компонентов нижнего кэша. Это позволяет полностью использовать кэш-память. Однако существует большая задержка доступа к памяти. [26]

Вышеупомянутые политики требуют соблюдения набора правил для их реализации. Если ни один из них не является принудительным, результирующая политика включения называется неисключительной неисключительной (ДЕВЯТЬ). Это означает, что кэш верхнего уровня может присутствовать или отсутствовать в кэше нижнего уровня. [21]

Написать политику [ править ]

Существуют две политики, которые определяют способ обновления измененного блока кэша в основной памяти: сквозная запись и обратная запись. [25]

В случае политики сквозной записи всякий раз, когда значение блока кэша изменяется, оно также модифицируется в иерархии памяти нижнего уровня. [27] Эта политика гарантирует безопасное хранение данных, поскольку они записываются по всей иерархии.

Однако в случае политики обратной записи измененный блок кэша будет обновлен в иерархии нижнего уровня только тогда, когда блок кэша будет исключен. «Грязный бит» прикрепляется к каждому блоку кеша и устанавливается всякий раз, когда блок кеша изменяется. [28] Во время вытеснения блоки с установленным грязным битом будут записаны в иерархию нижнего уровня. В соответствии с этой политикой существует риск потери данных, поскольку последняя измененная копия данных сохраняется только в кэше, и поэтому необходимо соблюдать некоторые методы исправления.

В случае записи, когда байт отсутствует в блоке кэша, байт может быть перенесен в кэш, как определено политикой выделения для записи или записи без выделения. [25] Политика выделения памяти для записи гласит, что в случае ошибки записи блок извлекается из основной памяти и помещается в кэш перед записью. [29] В политике записи без выделения памяти, если блок пропущен в кэше, он будет записывать в иерархию памяти нижнего уровня без извлечения блока в кэш. [30]

Распространенными комбинациями политик являются «блок записи», «выделение записи для записи» и «запись через запись без выделения памяти» .

[ править ]

Частный кеш назначается одному конкретному ядру процессора и не может быть доступен другим ядрам. В некоторых архитектурах каждое ядро имеет свой собственный частный кеш; это создает риск дублирования блоков в архитектуре кэш-памяти системы, что приводит к снижению использования емкости. Однако этот тип дизайна в многоуровневой архитектуре кэширования также может быть полезен для более низкой задержки доступа к данным. [25] [31] [32]

Общий кеш - это кеш, к которому могут обращаться несколько ядер. [33] Поскольку он является общим, каждый блок в кэше уникален и, следовательно, имеет более высокий процент попаданий, поскольку не будет дублированных блоков. Однако задержка доступа к данным может увеличиваться, поскольку несколько ядер пытаются получить доступ к одному и тому же кешу. [34]

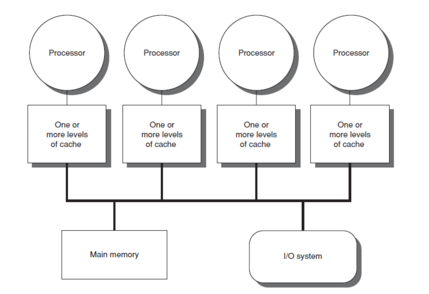

В многоядерных процессорах выбор конструкции кеш-памяти совместно или частным влияет на производительность процессора. [35] На практике кэш L1 верхнего уровня (или иногда L2) [36] [37] реализован как частный, а кеши нижнего уровня реализованы как совместно используемые. Эта конструкция обеспечивает высокую скорость доступа для кэшей высокого уровня и низкую частоту пропусков для кешей более низкого уровня. [35]

Последние модели реализации [ править ]

Микроархитектура Intel Broadwell (2014 г.) [ править ]

- Кэш L1 (инструкции и данные) - 64 КБ на ядро

- Кэш L2 - 256 КБ на ядро

- Кэш L3 - от 2 МБ до 6 МБ совместно

- Кэш L4 - 128 МБ eDRAM (только модели Iris Pro) [36]

Микроархитектура Intel Kaby Lake (2016 г.) [ править ]

- Кэш L1 (инструкции и данные) - 64 КБ на ядро

- Кэш L2 - 256 КБ на ядро

- Кэш L3 - от 2 МБ до 8 МБ [37]

Микроархитектура AMD Zen (2017 г.) [ править ]

- Кэш L1 - 32 КБ данных и 64 КБ инструкций на ядро, 4-полосный

- Кэш L2 - 512 КБ на ядро, включительно с 4 процессорами

- Кэш L3 - 4 МБ локальных и удаленных на 4-ядерный CCX, 2 CCX на чиплет, не включительно с 16 процессорами. До 16 МБ на ЦП настольных ПК и до 64 МБ на ЦП сервера

Микроархитектура AMD Zen 2 (2019) [ править ]

- Кэш L1 - 32 КБ данных и 32 КБ инструкций на ядро, 8-процессорный

- Кэш L2 - 512 КБ на ядро, включая 8 потоков

- Кэш L3 - 16 МБ локально на 4-ядерный CCX, 2 CCX на чиплет, не включительно с 16 процессорами. До 64 МБ на ЦП настольных ПК и 256 МБ на ЦП сервера

IBM Power 7 [ править ]

- Кэш L1 (инструкции и данные) - каждый с 64-ю банками, каждый банк имеет 2rd + 1wr порта 32 КБ, 8-сторонний ассоциативный, блок 128Б, запись через

- Кэш L2 - 256 кБ, 8-полосный, блок 128Б, обратная запись, включая L1, задержка доступа 2 нс

- Кэш L3 - 8 областей по 4 МБ (всего 32 МБ), локальная область 6 нс, удаленная 30 нс, каждая область 8-сторонняя ассоциативная, массив данных DRAM, массив тегов SRAM [39]

См. Также [ править ]

- Мощность7

- Микроархитектура Intel Broadwell

- Микроархитектура Intel Kaby Lake

- Кэш ЦП

- Иерархия памяти

- Задержка CAS

- Кэш (вычисления)

Ссылки [ править ]

- ^ Хеннесси, Джон L; Паттерсон, Дэвид А; Асанович, Крсте; Бакос, Джейсон Д; Колвелл, Роберт П.; Бхаттачарджи, Абхишек; Конте, Томас М; Дуато, Хосе; Франклин, Диана; Гольдберг, Дэвид; Джуппи, Норман П.; Ли, Шэн; Муралиманохар, Навин; Петерсон, Грегори Д. Пинкстон, Тимоти Марк; Ранганатан, Пракаш; Вуд, Дэвид Аллен; Янг, Клиффорд; Заки, Амр (2011). Компьютерная архитектура: количественный подход (шестое изд.). ISBN 978-0128119051. OCLC 983459758 .

- ^ «Кэш: зачем его выравнивать» (PDF) .

- ^ Рональд Д. Миллер; Ларс И. Эрикссон; Ли А. Флейшер, 2014. Электронная книга Миллера по анестезии. Elsevier Health Sciences. п. 75. ISBN 978-0-323-28011-2 .

- ^ Альберт Ю. Зомая, 2006. Справочник по природным и инновационным вычислениям: интеграция классических моделей с новыми технологиями. Springer Science & Business Media. п. 298. ISBN 978-0-387-40532-2 .

- ^ Ричард С. Дорф, 2018. Датчики, нанонаука, биомедицинская инженерия и инструменты: датчики, нанонаука, биомедицинская инженерия. CRC Press. п. 4. ISBN 978-1-4200-0316-1 .

- ^ Дэвид А. Паттерсон; Джон Л. Хеннесси, 2004. Компьютерная организация и дизайн: аппаратно-программный интерфейс, третье издание. Эльзевир. п. 552. ISBN 978-0-08-050257-1 .

- ^ "Сэр Морис Винсент Уилкс | Британский ученый-компьютерщик" . Британская энциклопедия . Проверено 11 декабря 2016 .

- ↑ Беркли, Джон Л. Хеннесси, Стэнфордский университет, и Дэвид А. Паттерсон, Калифорнийский университет. «Структура иерархии памяти - Часть 6. Intel Core i7, заблуждения и подводные камни» . EDN . Проверено 11 декабря 2016 .

- ^ Шейн Кук, 2012. Программирование CUDA: Руководство разработчика по параллельным вычислениям с графическими процессорами. Newnes. С. 107–109. ISBN 978-0-12-415988-4 .

- ^ Брюс Hellingsworth; Патрик Холл; Говард Андерсон; 2001. Высшая национальная вычислительная техника. Рутледж. С. 30–31. ISBN 978-0-7506-5230-8 .

- ^ Рита Саху, Гаган Саху. Infomatic Practices. Сарасвати Хаус Пвт Лтд., Стр. 1–. ISBN 978-93-5199-433-6 .

- ^ Филипп А. Лапланте; Сеппо Дж. Оваска; 2011. Проектирование и анализ систем реального времени: инструменты для практиков. Джон Вили и сыновья. С. 94–95. ISBN 978-1-118-13659-1 .

- ^ a b c Хеннесси и Паттерсон. Компьютерная архитектура: количественный подход . Морган Кауфманн . ISBN 9780123704900.

- ^ Четин Кая Koc, 2008. Cryptographic Engineering. Springer Science & Business Media. С. 479–480. ISBN 978-0-387-71817-0 .

- ^ Дэвид А. Паттерсон; Джон Л. Хеннесси; 2008. Компьютерная организация и дизайн: аппаратно-программный интерфейс. Морган Кауфманн. С. 489–492. ISBN 978-0-08-092281-2 .

- ^ Харви Г. Крагон, 2000. Компьютерная архитектура и реализация. Издательство Кембриджского университета. С. 95–97. ISBN 978-0-521-65168-4 .

- ^ Бейкер Мохаммад, 2013. Проектирование встроенной памяти для многоядерных процессоров и систем на кристалле. Springer Science & Business Media. С. 11–14. ISBN 978-1-4614-8881-1 .

- ^ Гайд, Уильям. «Как проектируются и строятся процессоры» . Техспот . Проверено 17 августа 2019 .

- ^ Vojin Г. Oklobdzija, 2017. Digital Design и изготовление. CRC Press. п. 4. ISBN 978-0-8493-8604-6 .

- ^ «Иерархия памяти» .

- ^ a b Солихин, Ян (2016). Основы параллельной многоядерной архитектуры . Чепмен и Холл. С. Глава 5: Введение в организацию иерархии памяти. ISBN 9781482211184.

- ^ Ян Солихин, 2015. Основы параллельной многоядерной архитектуры. CRC Press. п. 150. ISBN 978-1-4822-1119-1 .

- ^ Стив Хит, 2002. Проектирование встроенных систем. Эльзевир. п. 106. ISBN 978-0-08-047756-5 .

- ^ Алан Клементс, 2013. Компьютерная организация и архитектура: темы и вариации. Cengage Learning. п. 588. ISBN 1-285-41542-6 .

- ^ а б в г д Солихин, Ян (2009). Основы параллельной компьютерной архитектуры . Издательство Солихина. С. Глава 6: Введение в организацию иерархии памяти. ISBN 9780984163007.

- ^ «Оценка производительности эксклюзивных иерархий кэша» (PDF) .

- ^ Дэвид А. Паттерсон; Джон Л. Хеннесси; 2017. Компьютерная организация и дизайн RISC-V Edition: аппаратно-программный интерфейс. Elsevier Science. С. 386–387. ISBN 978-0-12-812276-1 .

- ^ Стефан Гёдекер; Адольфи Хойси; 2001. Оптимизация производительности численно интенсивных кодов. СИАМ. п. 11. ISBN 978-0-89871-484-5 .

- ^ Харви Г. Крагон, 1996. Системы памяти и конвейерные процессоры. Джонс и Бартлетт Обучение. п. 47. ISBN 978-0-86720-474-2 .

- ^ Дэвид А. Паттерсон; Джон Л. Хеннесси; 2007. Компьютерная организация и дизайн, переработанная печать, третье издание: аппаратно-программный интерфейс. Эльзевир. п. 484. ISBN 978-0-08-055033-6 .

- ^ «Программные методы для многоядерных систем с общим кешем» . 2018-05-24.

- ^ «Адаптивная схема разделения общего / частного кэша NUCA для многопроцессорных чипов» (PDF) . Архивировано из оригинального (PDF) 19 октября 2016 года.

- ^ Аканкша Джайн; Кальвин Лин; 2019. Политики замены кеша. Издатели Morgan & Claypool. п. 45. ISBN 978-1-68173-577-1 .

- ^ Дэвид Каллер; Джасвиндер Пал Сингх; Ануп Гупта; 1999. Параллельная компьютерная архитектура: аппаратно-программный подход. Издательство Gulf Professional Publishing. п. 436. ISBN 978-1-55860-343-1 .

- ^ a b Стивен В. Кеклер; Кунле Олукотун; Х. Питер Хофсти; 2009. Многоядерные процессоры и системы. Springer Science & Business Media. п. 182. ISBN 978-1-4419-0263-4 .

- ^ a b «Микроархитектура Intel Broadwell» .

- ^ a b "Микроархитектура Intel Kaby Lake" .

- ^ "Архитектура процессора Nehalem и платформ SMP Nehalem-EP" (PDF) . Архивировано из оригинального (PDF) 11 августа 2014 года.

- ^ «IBM Power7» .