Флэш АЦП

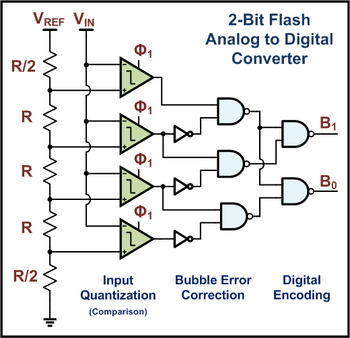

Флэш-АЦП (также известный как АЦП прямого преобразования ) представляет собой тип аналого -цифрового преобразователя , который использует линейную лестницу напряжения с компаратором на каждой «ступени» лестницы для сравнения входного напряжения с последовательными опорными напряжениями. Часто эти эталонные лестницы состоят из множества резисторов ; однако современные реализации показывают, что возможно и емкостное деление напряжения. Выход этих компараторов обычно подается на цифровой кодировщик, который преобразует входные данные в двоичное значение (собранные выходные данные компараторов можно рассматривать как унарное значение).

Преобразователи флэш-памяти чрезвычайно быстры по сравнению со многими другими типами АЦП, которые обычно сужают «правильный» ответ на нескольких этапах. По сравнению с ними, флэш-конвертер также довольно прост и, кроме аналоговых компараторов, требует только логики для окончательного преобразования в двоичный код .

Для лучшей точности перед входом АЦП часто вставляют схему отслеживания и удержания . Это необходимо для многих типов АЦП (например , АЦП последовательного приближения ), но для флэш-АЦП в этом нет реальной необходимости, потому что компараторы являются устройствами выборки.

Для флэш-преобразователя требуется огромное количество компараторов по сравнению с другими АЦП, особенно с увеличением точности. Для флэш-преобразователя требуются компараторы для n - битного преобразования. Размер, энергопотребление и стоимость всех этих компараторов делают флэш-преобразователи, как правило, непрактичными для точности, намного превышающей 8 бит (255 компараторов). Вместо этих компараторов большинство других АЦП заменяют более сложную логику и/или аналоговую схему, которую можно легче масштабировать для повышения точности .

Флэш-АЦП были реализованы во многих технологиях, от кремниевых биполярных (BJT) и комплементарных полевых транзисторов на основе оксида металла ( CMOS ) до редко используемых технологий III-V . Часто этот тип АЦП используется в качестве первой проверки аналоговой схемы среднего размера.

Самые ранние реализации состояли из эталонной лестницы из хорошо согласованных резисторов, подключенных к эталонному напряжению. Каждый отвод резисторной лестницы используется для одного компаратора, которому, возможно, предшествует каскад усиления , и, таким образом, генерирует логический 0 или 1 в зависимости от того, выше или ниже измеренное напряжение опорного напряжения отвода резистора . Причина добавления усилителя двояка: он усиливает разность напряжений и, таким образом, подавляет смещение компаратора, а также сильно подавляется шум отдачи компаратора по направлению к эталонной лестнице. Обычно производятся проекты от 4-битных до 6-битных, а иногда и 7-битных.