Intel 5 Series - это вычислительная архитектура, представленная в 2008 году, которая повышает эффективность и балансирует использование каналов связи на материнской плате . Архитектура состоит в основном из центрального процессора (ЦП) (подключенного к видеокарте и памяти) и одного набора микросхем (подключенного к компонентам материнской платы). Все коммуникации и действия материнской платы связаны с этими двумя устройствами.

Архитектура является продуктом изменений, внесенных в Intel 4 Series для обеспечения более производительных материнских плат при сохранении эффективности и низкого энергопотребления. Изменения касаются набора микросхем и дизайна процессора, а также изменения порядка функций и контроллеров. Результат - первое серьезное изменение за многие годы вычислений.

Концепция дизайна [ править ]

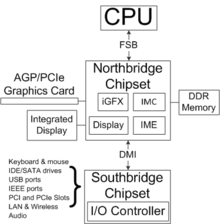

Концепция архитектуры заключалась в улучшении механики материнской платы, чтобы идти в ногу с процессором, поскольку он набирал большую скорость и увеличивал количество ядер. В предыдущей архитектуре ЦП активно взаимодействовал с центральным компонентом материнской платы, чипсетом северного моста , поскольку он был посредником между ЦП, памятью и, в большинстве случаев, видеокартой. ЦП будет связываться с набором микросхем северного моста, когда ему нужны данные из памяти или когда необходимо вывести графику на дисплей. Такое расположение привело к тому, что канал связи, известный как внешняя шина(ФСБ) будет активно использоваться. Вскоре либо ФСБ выйдет на полную мощность, либо будет работать неэффективно с большим количеством ядер. Когда контроллер памяти и / или графическое ядро перемещаются в процессор, использование отдельных наборов микросхем материнской платы для этих функций уменьшается.

Пик Козерога [ править ]

Набор микросхем Ibex Peak включает только концентратор контроллера платформы (PCH) для каждой модели, который обеспечивает периферийные соединения и контроллеры дисплея для ЦП со встроенной графикой через гибкий интерфейс дисплея (за исключением P-моделей). Кроме того, PCH подключается к CPU через Direct Media Interface (DMI).

Используя преимущества процессоров Intel Nehalem со встроенной графикой и портами PCI Express , Intel Management Engine (ME) и контроллер дисплея для интегрированной графики, когда-то размещенные в северном мосту, перемещаются в концентратор контроллера платформы (PCH). Функция концентратора контроллера ввода-вывода (ICH) интегрирована в PCH, что устраняет необходимость в отдельных северном и южном мостах .

| Набор микросхем | Кодовое название | Номер sSpec | Номера деталей | Дата выпуска | Интерфейс шины | Скорость соединения [a] | PCI Express полосы | PCI | SATA | USB | Поддержка ПИИ | TDP |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 3 Гбит / с | v2.0 | |||||||||||

| H55 | Пик Козерога [1] [2] | SLGZX (B3) | БД82Н55 (ПЧ) | Январь 2010 г. | DMI | 2 ГБ / с | 6 PCIe 2.0 при 2,5 ГТ / с | да | 6 портов | 12 портов | да | 5,2 Вт |

| P55 | SLH24 (B3), SLGWV (B2) | БД82П55 (ПЧ) | Сентябрь 2009 г. | 8 PCIe 2.0 при 2,5 ГТ / с | 14 портов | Нет | 4,7 Вт | |||||

| H57 | SLGZL (B3) | БД82Н57 (ПЧ) | Январь 2010 г. | да | 5,2 Вт | |||||||

| Q57 | SLGZW (B3) | BD82Q57 (PCH) | 5,1 Вт |

| Модель | Верхняя маркировка |

|---|---|

| PM55 Экспресс | BD82PM55 |

| QM57 Экспресс | BD82QM57 |

| HM55 Экспресс | BD82HM55 |

| HM57 Экспресс | BD82HM57 |

| QS57 Экспресс | BD82QS57 |

| Модель | Верхняя маркировка | Fab | Версия прошивки ME | PCIe |

|---|---|---|---|---|

| 3400 | BD3400 | 65 нм | 6.0 | 2.0 |

| 3420 | BD3420 | |||

| 3450 | BD3450 |

Тайлерсбург [ править ]

Tylersburg семейство наборов микросхем для сокета LGA 1366 с поддержкой процессоров с контроллерами памяти тройным канала. В отличие от наборов микросхем Ibex Peak , семейство наборов микросхем Tylersburg не включает PCH, а концентратор ввода-вывода в основном предоставляет дополнительные порты PCI Express 2.0. Периферийные соединения обеспечиваются концентратором контроллера ввода-вывода (ICH), подключенным к интерфейсу DMI. Модули ввода-вывода Intel серии 5 поддерживают ICH10, а модули ввода-вывода Intel серии 5500 поддерживают ICH9 или ICH10.

Одно гнездо Nehalem основанное чипсетом [ править ]

| Набор микросхем | Кодовое название | Номер sSpec | Номера деталей | Дата выпуска | Разъем | Интерфейс шины | PCI Express полосы | PCI | Поддержка Intel VT-d | SATA | USB | Поддержка ПИИ | TDP | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 6 Гбит / с | 3 Гбит / с | v3.0 | v2.0 | ||||||||||||

| X58 1 | Тайлерсбург | SLGBT (B2), SLGMX (B3), SLH3M (C2) | AC82X58 (IOH) | Ноябрь 2008 г. | LGA 1366 | QPI | 36 × PCIe 2.0 (IOH); 6 × PCIe 1.1 (ICH) | да | да | Никто | 6 портов | Никто | 12 портов | Нет | 28,6 Вт 2 |

- 1 Nehalem перемещает контроллер памяти в процессор, в результате чего северный мост устарел . Несмотря на это, LGA 1366 по-прежнему имеет северный и южный мосты. X58 IOH действует как мост между QPI и периферийными устройствами PCI Express и DMI с южным мостом ICH10 / ICH10R .

- 2 X58 TDP включает X58 IOH TDP в дополнение к ICH10 / ICH10R TDP.

Двойной разъем Nehalem -Xeon чипсеты [ править ]

Xeon на базе Nehalem для двухпроцессорных систем, первоначально представленные как серия Xeon 55xx, имеют совершенно иную структуру системы: контроллеры памяти находятся на ЦП, а ЦП могут обмениваться данными друг с другом как одноранговые узлы, не используя набор микросхем. Это означает , что 5500 и 5520 (первоначальное кодовое название Tylersburg-EP), по существу , наборы микросхем QPI с PCI Express интерфейсами; 5520 больше предназначен для графических рабочих станций, а 5500 - для серверов, которым не требуется большое количество подключений PCI Express.

| Название запуска | Кодовое название | QPI порты | QPI скорость | Быстрый ввод / вывод | IOCH | Другие особенности | Верхняя маркировка |

|---|---|---|---|---|---|---|---|

| 5500 | Тайлерсбург-24С, Тайлерсбург -24Д [3] | 1, 2 | 4,8, 5,86 или 6,4 ГТ / с | 1 × 16 PCIe Gen 2, 2 × 4 PCIe Gen 1 для подключения к южному мосту | ICH10 (также возможно ICH9) | Интегрированный механизм управления с собственным 100 Мбит Ethernet [4] | AC5500 SLGMT 901036 (B-3), AC5500 SLH3N 904728 (C-2) |

| 5520 | Тайлерсбург-36С, Тайлерсбург-36Д | 1, 2 | 4,8, 5,86 или 6,4 ГТ / с | 2 × 16 PCIe Gen 2, 1 × 4 PCIe Gen 1 для подключения к южному мосту | ICH10 (также возможно ICH9) | Интегрированный механизм управления с собственным 100 Мбит Ethernet [4] | AC5520 SLGMU 901037 (B-3), AC5520 SLH3P 904729 (C-2) |

См. Также [ править ]

- Intel P55

- Intel X58

Заметки [ править ]

- ^ Суммарная скорость для обоих направлений

Ссылки [ править ]

- ^ Набор микросхем Intel серии 5

- ^ Набор микросхем Mobile Intel серии 5

- ^ http://www.guru3d.com/articles-pages/intel-x58-extreme-dx58so-motherboard-review,2.html

- ^ a b http://www.intel.com/content/dam/www/public/us/en/documents/datasheets/5520-5500-chipset-ioh-datasheet.pdf

Внешние ссылки [ править ]

Пик Козерога [ править ]

- Intel 5 серии: H55 , H57 , P55 , Q57

- Мобильный Intel серии 5: HM55 , HM57 , PM55 , QM57 , QS57

- Обзор наборов микросхем Intel 3400 и 3420

- Набор микросхем Intel серии 5 и набор микросхем Intel серии 3400

- Поддержка набора микросхем Intel серии 5

- Intel "Пик Козерога"

Тайлерсбург [ править ]

- Набор микросхем Intel X58 Express

- Intel серии 5500 : 5500 , 5520

- Наборы микросхем Intel 5500 и 5520