| Основная информация | |

|---|---|

| Запущен | 2007 г. |

| Общий производитель (и) | |

| Представление | |

| Максимум. Тактовая частота процессора | От 600 МГц до 900 МГц |

| Архитектура и классификация | |

| Мин. размер элемента | От 45 нм до 90 нм |

| Физические характеристики | |

| Ядра |

|

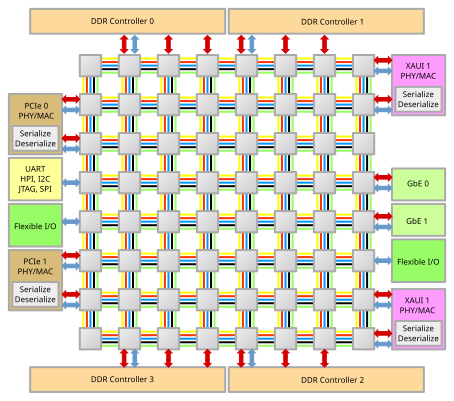

TILE64 [1] - многоядерный процессор VLIW ISA производства Tilera . Он состоит из ячеистой сети из 64 «плиток», где каждая плитка содержит универсальный процессор , кэш и неблокирующий маршрутизатор , который плитка использует для связи с другими плитками на процессоре.

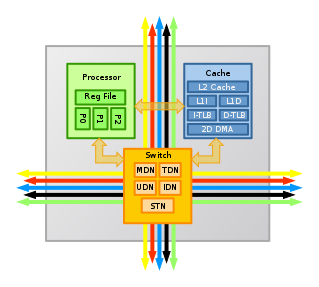

Короткий конвейер , упорядоченные ядра с тремя задачами реализуют набор инструкций VLIW, вдохновленный MIPS [2] . Каждое ядро имеет регистровый файл и три функциональных блока: два блока целочисленной арифметической логики и блок загрузки-сохранения . Каждое из ядер («плитка») имеет свои собственные кеши L1 и L2 плюс общий виртуальный кэш L3, который является совокупностью всех кешей L2. [3] Ядро может запускать полную операционную систему самостоятельно, или несколько ядер могут использоваться для запуска симметричной многопроцессорной операционной системы.

TILE64 имеет четыре контроллера DDR2 , два 10-гигабитных интерфейса Ethernet , два четырехполосных интерфейса PCIe и «гибкий» интерфейс ввода / вывода, который можно программно настроить для обработки ряда протоколов. Процессор изготовлен по 90-нм техпроцессу и работает на частотах от 600 до 900 МГц.

По словам технического директора и соучредителя Ананта Агарвала , Tilera нацелит этот чип на рынок сетевого оборудования и цифрового видео, где требования к вычислительной обработке высоки. [4]

Поддержка архитектуры TILE64 была добавлена в ядро Linux версии 2.6.36 [5], но была исключена в версии ядра 4.16. [6] Существует неофициальная серверная часть LLVM для Tilera. [7]

Ссылки [ править ]

- ^ Кеклер, Стивен В .; Олюкотун, Кунле; Питер Хофсти, Х. (29 августа 2009 г.). Многоядерные процессоры и системы - Google Книги . ISBN 9781441902634. CS1 maint: discouraged parameter (link)

- ^ https://stackoverflow.com/questions/6515358/what-instruction-set-is-used-by-tilera-microprocessors

- ↑ Кингман, Генри (20 августа 2007 г.). «Многоядерный процессор работает под управлением Linux» . linuxdevices.com. Архивировано из оригинального 6 -го сентября 2012 года. CS1 maint: discouraged parameter (link)

- ^ Boslet, Марк (20 августа 2007). «Стартап Tilera представит 64-ядерный чип» . Новости Сан-Хосе Меркьюри . Архивировано из оригинального 12 ноября 2007 года.

- ^ "Поддержка архитектуры Tilera" . Ядро новичков. 20 октября 2010 г.

- ^ Саймон Sharwood (3 апреля 2018). «Прибывает Linux 4.16, стирает восемь процессоров и продолжает плавить Meltdown» . theregister.co.uk . Публикация ситуации. Архивировано из оригинала 3 апреля 2018 года . Проверено 3 апреля 2018 года . CS1 maint: discouraged parameter (link)

- ^ Опубликована серверная часть Tilera TILE64 для LLVM // Phoronix , 6 сентября 2012 г.

Внешние ссылки [ править ]

- Сайт Тилера

- Стартап MIT поднимает планку многоядерных процессоров с новым 64-ядерным процессором

- Производители микросхем стремятся очистить пути к данным на archive.today (архивировано 19 января 2013 г. )