Множитель Dadda является аппаратный умножитель дизайн изобретен компьютер ученого Луиджи Dadda в 1965 г. [1] Это похоже на Wallace мультипликатор , но он немного быстрее (для всех размеров операндов) и требует меньше ворота (для всех , кроме самых маленьких операнд размеры). [2]

Фактически, множители Дадды и Уоллеса имеют одинаковые три шага для двух битовых строк и длины и соответственно:

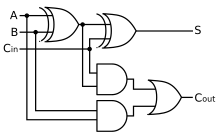

- Умножение ( логическое И ) каждого бита на каждый бит дает результаты, сгруппированные по весу в столбцах.

- Уменьшайте количество частичных произведений путем добавления полных и половинных сумматоров до тех пор, пока у нас не останется не более двух битов каждого веса.

- Сложите конечный результат обычным сумматором.

Как и в случае умножителя Уоллеса, произведения умножения на первом этапе имеют разные веса, отражающие величину исходных значений битов при умножении. Например, произведение бит имеет вес .

В отличие от множителей Уоллеса, которые максимально уменьшают на каждом слое, множители Дадда пытаются минимизировать количество используемых вентилей, а также задержку ввода / вывода. Из-за этого умножители Дадды имеют менее затратную фазу сокращения, но конечные числа могут быть на несколько бит длиннее, что требует немного больших сумматоров.

Описание [ править ]

Чтобы получить более оптимальный конечный продукт, структура процесса восстановления регулируется немного более сложными правилами, чем в множителях Уоллеса.

Прогрессирование сокращения контролируется последовательностью максимальной высоты , определяемой:

Это дает такую последовательность:

Начальное значение выбирается как наибольшее значение, такое, что , где и - количество битов во входном множимом и множителем. Меньшая из двух битовых длин будет максимальной высотой каждого столбца весов после первого этапа умножения. Для каждого этапа сокращения целью алгоритма является уменьшение высоты каждого столбца так, чтобы оно было меньше или равно значению .

Для каждого этапа от уменьшите каждый столбец, начиная с столбца с наименьшим весом, в соответствии со следующими правилами:

- Если столбец не требует уменьшения, перейдите к столбцу

- Если добавить два верхних элемента в полусумматор, поместив результат в нижнюю часть столбца, а перенос в верхнюю часть столбца , затем переместитесь в столбец

- В противном случае добавьте три верхних элемента в полный сумматор, поместив результат в нижнюю часть столбца, а перенос в верхнюю часть столбца , перезапустите с шага 1

Пример алгоритма [ править ]

Пример на соседнем изображении иллюстрирует уменьшение множителя 8 × 8, объясненное здесь.

Начальное состояние выбрано как , наибольшее значение меньше 8.

Стадия ,

- все меньше или равны шести битам по высоте, поэтому никаких изменений не вносится

- , поэтому применяется полусумматор, уменьшающий его до шести бит и добавляющий его бит переноса к

- включая бит переноса из , поэтому мы применяем полный сумматор и полусумматор, чтобы уменьшить его до шести бит

- включая два бита переноса из , поэтому мы снова применяем полный сумматор и полусумматор, чтобы уменьшить его до шести бит

- включая два бита переноса из , поэтому мы применяем один полный сумматор и уменьшаем его до шести бит

- все меньше или равны шести битам в высоту, включая биты переноса, поэтому никаких изменений не производится

Стадия ,

- все меньше или равны четырем битам по высоте, поэтому никаких изменений не вносится

- , поэтому применяется полусумматор, уменьшающий его до четырех бит и добавляющий его бит переноса к

- включая бит переноса из , поэтому мы применяем полный сумматор и полусумматор, чтобы уменьшить его до четырех бит

- включая предыдущие биты переноса, поэтому мы применяем два полных сумматора, чтобы уменьшить их до четырех бит

- включая предыдущие биты переноса, поэтому мы применяем полный сумматор, чтобы уменьшить его до четырех бит

- все меньше или равны четырем битам по высоте, включая биты переноса, поэтому никаких изменений не производится

Стадия ,

- все меньше или равны трем битам по высоте, поэтому никаких изменений не вносится

- , поэтому применяется полусумматор, уменьшающий его до трех бит и добавляющий его бит переноса к

- включая предыдущие биты переноса, поэтому мы применяем один полный сумматор, чтобы уменьшить их до трех бит

- все меньше или равны трем битам по высоте, включая биты переноса, поэтому никаких изменений не производится

Стадия ,

- все меньше или равны двум битам по высоте, поэтому никаких изменений не вносится

- , поэтому применяется полусумматор, уменьшающий его до двух бит и добавляющий его бит переноса к

- включая предыдущие биты переноса, поэтому мы применяем один полный сумматор, чтобы уменьшить их до двух бит

- включая бит переноса из , поэтому никаких изменений не вносится

Добавление

На выходе последнего этапа остается 15 столбцов высотой два или меньше, которые можно передать в стандартный сумматор.

См. Также [ править ]

- Алгоритм умножения Бута

- Слитное умножение – сложение

- Дерево Уоллеса

- Алгоритм BKM для комплексных логарифмов и экспонент

- Умножение Кочанского для модульного умножения

Ссылки [ править ]

- ^ Dadda, Luigi (май 1965 г.). «Некоторые схемы параллельных умножителей». Alta Frequenza . 34 (5): 349–356.

- ^ Таунсенд, Уитни Дж .; Шварцлендер младший, граф Э .; Авраам, Джейкоб А. (декабрь 2003 г.) [2003-08-06]. «Сравнение задержек множителя Дадды и Уоллеса» (PDF) . Расширенные алгоритмы, архитектуры и реализации SPIE XIII . Международное общество . DOI : 10.1117 / 12.507012 . Архивировано (PDF) из оригинала на 2018-07-16 . Проверено 16 июля 2018 .

Дальнейшее чтение [ править ]

- Савард, Джон Дж. Г. (2018) [2006]. «Продвинутые арифметические методы» . квадиблок . Архивировано 3 июля 2018 года . Проверено 16 июля 2018 .