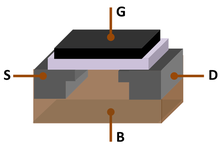

МОП-транзистор, показывающий клеммы затвора (G), корпуса (B), истока (S) и стока (D). Ворота отделены от корпуса изоляционным слоем (розового цвета). | |

| Принцип работы | Полупроводник |

|---|---|

| Изобретенный | 1959 г. |

| Первая продукция | 1960 г. |

| Конфигурация контактов | затвор (G), корпус (B), исток (S) и сток (D) |

Металл-оксид-полупроводник полевой транзистор ( МОП - транзистор , МОП - транзистор , или МОП - полевой транзистор ), также известный как металл-оксид-кремниевый транзистор ( МОП - транзистор или МОП ), [1] представляет собой тип с изолированным затвором полевой транзистор , который изготавливают с помощью контролируемого окисления в виде полупроводника , обычно кремния . Напряжение закрытого затвора определяет электропроводность устройства; эта способность изменять проводимость в зависимости от приложенного напряжения может быть использована дляусиление или переключение электронных сигналов .

МОП-транзистор был изобретен Мохамедом М. Аталлой и Давоном Кангом в Bell Labs в 1959 году и впервые представлен в 1960 году. Это основной строительный блок современной электроники и наиболее часто производимое устройство в истории, общая стоимость которого оценивается в 13 секстиллионов. (1,3 × 10 22 ) полевых МОП-транзисторов, изготовленных в период с 1960 по 2018 гг. [2] Это доминирующее полупроводниковое устройство в цифровых и аналоговых интегральных схемах (ИС) [3] и наиболее распространенное устройство питания . [4] Это компактный транзистор , который был миниатюризирован и серийно производился для широкого спектра применений , революционизировал электронную промышленность и мировую экономику и стал центральным элементом цифровой революции , эпохи кремния и информационного века.. Масштабирование и миниатюризация полевых МОП-транзисторов стимулировали быстрый экспоненциальный рост электронных полупроводниковых технологий с 1960-х годов и позволяют создавать ИС высокой плотности, такие как микросхемы памяти и микропроцессоры . MOSFET считается «рабочей лошадкой» электронной промышленности.

Ключевым преимуществом полевого МОП-транзистора является то, что он почти не требует входного тока для управления током нагрузки по сравнению с транзисторами с биполярным переходом (BJT). В полевом МОП-транзисторе в режиме улучшения напряжение, приложенное к выводу затвора, может увеличить проводимость из состояния «нормально выключено». В режиме истощения MOSFET напряжение, приложенное к затвору, может снизить проводимость от «нормально включенного» состояния. [5] MOSFET-транзисторы также обладают высокой масштабируемостью с увеличением миниатюризации и могут быть легко уменьшены до меньших размеров. Они также имеют более высокую скорость переключения (идеально для цифровых сигналов.), гораздо меньшего размера, потребляют значительно меньше энергии и обеспечивают гораздо более высокую плотность (идеально для крупномасштабной интеграции ) по сравнению с BJT. MOSFET-транзисторы также дешевле и имеют относительно простые этапы обработки, что приводит к высокому выходу продукции .

МОП-транзисторы могут быть изготовлены как часть интегральных схем МОП-транзисторов или как дискретные МОП-транзисторы (например, силовые МОП-транзисторы ) и могут иметь форму транзисторов с одним или несколькими затворами . Поскольку полевые МОП-транзисторы могут быть изготовлены из полупроводников p-типа или n-типа ( логика PMOS или NMOS соответственно), дополнительные пары полевых МОП-транзисторов могут использоваться для создания схем переключения с очень низким энергопотреблением : логика CMOS (дополнительная МОП).

Название «металл – оксид – полупроводник» (МОП) обычно относится к металлическому затвору , оксидной изоляции и полупроводнику (обычно кремнию). [1] Однако «металл» в названии MOSFET иногда используется неправильно, потому что материал затвора также может быть слоем поликремния (поликристаллического кремния). Наряду с оксидом можно использовать различные диэлектрические материалы с целью получения прочных каналов с меньшими приложенными напряжениями. МОП - конденсатор также является частью структуры МОП - транзистор.

Ранняя история [ править ]

Фон [ править ]

Основной принцип полевого транзистора (FET) был впервые предложен австрийским физиком Юлиусом Эдгаром Лилиенфельдом в 1926 году, когда он подал первый патент на полевой транзистор с изолированным затвором. [6] В течение следующих двух лет он описал различные структуры полевых транзисторов. В его конфигурации алюминий образовывал металл, а оксид алюминия - оксид, а сульфид меди использовался в качестве полупроводника . Однако построить практичный рабочий прибор ему так и не удалось. [7] Концепция полевого транзистора позже была выдвинута в теории немецким инженером Оскаром Хейлем в 1930-х годах и американским физиком Уильямом Шокли в 1940-х годах.[8] В то время не существовало работающего практического полевого транзистора, и ни одно из этих ранних предложений полевого транзистора не касалось термически окисленного кремния. [7]

Полупроводниковые компании первоначально сосредоточились на транзисторах с биполярным переходом (BJT) в первые годы полупроводниковой промышленности . Однако переходной транзистор был относительно громоздким устройством, которое было трудно производить в серийном производстве , что ограничивало его ряд специализированных применений. Полевые транзисторы теоретизировались как потенциальная альтернатива переходным транзисторам, но исследователи не смогли создать практические полевые транзисторы, в основном из-за проблемного барьера поверхностного состояния, который не позволял внешнему электрическому полю проникать в материал. [9] В 1950-х годах исследователи в значительной степени отказались от концепции полевого транзистора и вместо этого сосредоточились на технологии BJT. [10]

В 1955 году Карл Фрош и Линкольн Деррик случайно покрыли поверхность кремниевой пластины слоем диоксида кремния . При последующей экспериментальной характеристике этого оксидного слоя они обнаружили, что он блокирует проникновение определенных примесей в кремниевую пластину (несмотря на то, что разрешены другие), и тем самым обнаружили пассивирующий эффект поверхностного окисления.слой на этом полупроводнике. Их дальнейшая работа продемонстрировала вытравливание небольших отверстий в оксидном слое для диффузии легирующих добавок в точно контролируемые области кремниевой пластины. В 1957 году они опубликовали исследовательскую работу и запатентовали свою методику, обобщающую их работу. Разработанный ими метод известен как маскирование диффузии оксидов, которое позже будет использоваться при производстве полевых МОП-транзисторов. В Bell Labs сразу же осознали важность техники Фроша, поскольку оксиды кремния намного более стабильны, чем оксиды германия, имеют лучшие диэлектрические свойства и в то же время могут использоваться в качестве диффузионной маски. Результаты их работы распространились по Bell Labs в форме записок BTL до того, как были опубликованы в 1957 году. В Shockley Semiconductor.В декабре 1956 года Шокли разослал препринт своей статьи всем своим руководящим сотрудникам, включая Джин Хорни . [9] [11] [12]

Изобретение [ править ]

Мохамед М. Аталла из Bell Labs в конце 1950-х годов занимался проблемой поверхностных состояний. Он поднял работу Фроша на окисление, пытаясь пассивации поверхности из кремния через формирование оксидного слоя над ним. Он думал , что растет очень тонкий высокое качество термически выращенного Si O 2 на верхней части чистой кремниевой пластины нейтрализует поверхностные состояния достаточно , чтобы сделать практическое рабочее полевой транзистор. Он написал свои открытия в своих записках BTL в 1957 году, прежде чем представить свою работу на собрании Электрохимического общества в 1958 году. [13] [14] [15] [16] [8]Это было важным событием, которое позволило использовать технологию MOS и кремниевые интегральные схемы (IC). [17] В следующем году Джон Л. Молл описал МОП-конденсатор в Стэнфордском университете . [18] Сотрудникам Аталлы, Дж. Р. Лигенце и В. Г. Спитцеру, которые изучили механизм термически выращенных оксидов, удалось изготовить высококачественный пакет Si / SiO 2 , [7] с Аталлой и Кангом, использовавшими их результаты. [19] [20]

МОП - транзистор был изобретен , когда Мохамед Atalla и Давон Канг [14] [13] успешно изготовлен первое устройство рабочего полевого МОП - транзистора в ноябре 1959 г. [21] устройство покрыто двумя патентами, каждый из которых поданы отдельно от Atalla и Kahng в марте 1960 г. [ 22] [23] [24] [25] Они опубликовали свои результаты в июне 1960 года [26] на конференции по твердотельным устройствам, состоявшейся в Университете Карнеги-Меллона . [27] В том же году Аталла предложила использовать МОП-транзисторы для создания микросхем МОП-интегральных схем (МОП-ИС), отметив простоту изготовления МОП-транзисторов. [9]

Коммерциализация [ править ]

Преимущество полевого МОП-транзистора состояло в том, что он был относительно компактен и прост в массовом производстве по сравнению с конкурирующим транзистором с плоским переходом [28], но полевой МОП-транзистор представлял собой радикально новую технологию, внедрение которой потребовало бы отказа от прогресса, достигнутого Беллом. выполнен на биполярном переходном транзисторе (BJT). MOSFET также изначально был медленнее и менее надежен, чем BJT. [29]

В начале 1960-х годов программы исследования технологии МОП были созданы Fairchild Semiconductor , RCA Laboratories , General Microelectronics (во главе с бывшим инженером Fairchild Фрэнком Ванлассом ) и IBM . [30] В 1962 году Стив Р. Хофштейн и Фред П. Хейман из RCA создали первый чип интегральной схемы МОП . В следующем году они собрали все предыдущие работы по полевым транзисторам и представили теорию работы полевых транзисторов. [31] CMOS была разработана Chih-Tang Sah и Frank Wanlass в Fairchild в 1963 году. [32] Первая интегральная схема CMOS была позже построена в 1968 году.Альберт Медвин . [33]

Первое официальное публичное объявление о существовании MOSFET в качестве потенциальной технологии было сделано в 1963 году. Впервые он был коммерциализирован General Microelectronics в мае 1964 года, а затем Fairchild в октябре 1964 года. Первый контракт GMe на MOS был заключен с NASA , которое использовало MOSFET для космических кораблей и спутники в программе платформы межпланетного мониторинга (IMP) и программе Explorers . [30] Первые полевые МОП-транзисторы, продаваемые General Microelectronics и Fairchild, были устройствами с p-каналом ( PMOS ) для приложений логики и переключения. [8] К середине 1960-х RCAиспользовали полевые МОП-транзисторы в своих потребительских товарах, включая FM-радио , телевидение и усилители . [34] В 1967 году исследователи Bell Labs Роберт Кервин, Дональд Кляйн и Джон Сарас разработали МОП-транзистор с самовыравнивающимся затвором (кремниевым затвором), который исследователи Fairchild Федерико Фаггин и Том Кляйн адаптировали для интегральных схем в 1968 году [35].

MOS Revolution [ править ]

Разработка полевых МОП-транзисторов привела к революции в электронных технологиях, названной «революцией МОП-транзисторов» [36] или революцией «МОП-транзисторы» [37], которая способствовала технологическому и экономическому росту ранней полупроводниковой промышленности .

Влияние MOSFET стало коммерчески значимым с конца 1960-х годов. [38] Это привело к революции в электронной промышленности , которая с тех пор практически во всех отношениях повлияла на повседневную жизнь. [39] Изобретение полевого МОП-транзистора было названо рождением современной электроники [40] и сыграло центральную роль в революции микрокомпьютеров. [41]

Важность [ править ]

MOSFET составляет основу современной электроники [42] и является основным элементом большинства современного электронного оборудования . [43] Это самый распространенный транзистор в электронике, [13] и наиболее широко используемый полупроводниковый прибор в мире. [44] Он был описан как «рабочая лошадка электронной промышленности» [45] и «базовая технология» конца 20-го - начала 21-го веков. [10] Масштабирование и миниатюризация MOSFET (см. Список примеров шкалы полупроводников ) были основными факторами быстрого экспоненциального роста электронных полупроводников.Технология с 1960 года , [46] , как быстрое миниатюризация МОП - транзисторов был в значительной степени ответственен за увеличением плотности транзистора , повышение производительности и снижение потребляемой мощности от интегральной схемы чипов и электронных устройств , начиная с 1960 - х годов. [47]

МОП - транзисторы способны высокой масштабируемости ( закон Мура и Dennard масштабирования ), [48] с ростом миниатюризации , [49] и может быть легко уменьшено до меньших размеров. [50] Они потребляют значительно меньше энергии и имеют гораздо более высокую плотность, чем биполярные транзисторы. [51] Таким образом, полевые МОП-транзисторы имеют гораздо меньший размер, чем БЮТ [52] , [52] примерно в двадцатую часть размера к началу 1990-х годов. [52] МОП-транзисторы также имеют более высокую скорость переключения [4] с быстрым электронным переключением, что делает их идеальными для генерации последовательностей импульсов., [53] основа для цифровых сигналов . [54] [55] в отличие от BJT, которые более медленно генерируют аналоговые сигналы, напоминающие синусоидальные волны . [53] МОП-транзисторы также дешевле [56] и имеют относительно простые этапы обработки, что приводит к высокому выходу продукции . [50] МОП - транзисторы , таким образом , позволяют крупномасштабной интеграции (LSI), и идеально подходят для цифровых схем , [57] , а также линейные аналоговые схемы . [53]

МОП - транзистор по - разному описывается как наиболее важным транзистор , [3] , наиболее важное устройство в электронной промышленности, [58] , возможно, самые важное устройство в компьютерной индустрии , [59] один из самых важных событий в полупроводниковой технологии, [60] и, возможно, самое важное изобретение в электронике. [61] MOSFET - транзистор был основным строительным блоком современных цифровой электроники , [10] во время цифровой революции , [62] информационная революция , информационный век ,[63] и кремниевый возраст . [64] [65] МОП-транзисторы были движущей силой компьютерной революции и технологий, которые она сделала. [66] [67] [68] Быстрый прогресс электронной промышленности в конце 20-го - начале 21-го веков был достигнут за счет быстрого масштабирования полевых МОП-транзисторов ( масштабирование Деннарда и закон Мура ) до уровня наноэлектроники в начале 21-го века. [69] MOSFET произвел революцию в мире в век информации, благодаря своей высокой плотности, позволяющей компьютерусуществовать на нескольких небольших микросхемах IC, а не заполнять комнату [70], а позже сделать возможными цифровые коммуникационные технологии, такие как смартфоны . [66]

MOSFET - это наиболее широко производимое устройство в истории. [71] [72] Годовой объем продаж МОП-транзисторов на 2015 год составил 295 миллиардов долларов . [73] В период с 1960 по 2018 год было произведено 13 секстиллионов МОП-транзисторов, что составляет не менее 99,9% всех транзисторов. [71] Цифровые интегральные схемы, такие как микропроцессоры и устройства памяти, содержат от тысяч до миллиардов интегрированных полевых МОП-транзисторов на каждом устройстве, обеспечивая основные функции переключения, необходимые для реализации логических вентилей. и хранение данных. Существуют также устройства памяти , которые содержат , по меньшей мере триллион МОП - транзисторов, например, 256 Гб MicroSD карты памяти , большие , чем число звезд в Млечном Пути галактики . [45] По состоянию на 2010 г. принципы работы современных полевых МОП-транзисторов остались в основном такими же, как и у оригинальных полевых МОП-транзисторов, впервые продемонстрированных Мохамедом Аталлой и Давоном Кангом в 1960 г. [74] [75]

Управление по патентам и товарным знакам США называет MOSFET «революционным изобретением, которое изменило жизнь и культуру во всем мире» [66], а Музей компьютерной истории считает его «безвозвратным изменением человеческого опыта». [10] MOSFET также послужил основой для достижений, получивших Нобелевскую премию, таких как квантовый эффект Холла [76] и устройство с зарядовой связью (CCD), [77], хотя сам MOSFET никогда не присуждался Нобелевской премии. [78] В 2018 году записку о Джек Килби «s Нобелевской премии по физикеЧто касается его участия в изобретении интегральной схемы, Шведская королевская академия наук особо упомянула полевой МОП-транзистор и микропроцессор как другие важные изобретения в развитии микроэлектроники . [79] MOSFET также включен в список основных этапов развития электроники IEEE [80], а его изобретатели Мохамед Аталла и Давон Канг вошли в Национальный зал славы изобретателей в 2009 году. [13] [14]

Состав [ править ]

Обычно предпочтительным полупроводником является кремний . В последнее время некоторые производители микросхем, в первую очередь IBM и Intel , начали использовать химическое соединение кремния и германия ( SiGe ) в каналах MOSFET. К сожалению, многие полупроводники с лучшими электрическими свойствами, чем кремний, такие как арсенид галлия , не образуют хороших границ раздела полупроводник-изолятор и поэтому не подходят для полевых МОП-транзисторов. Исследования продолжаются [ когда? ] по созданию изоляторов с приемлемыми электрическими характеристиками на других полупроводниковых материалах.

Чтобы преодолеть увеличение потребления энергии из-за утечки тока затвора, вместо диоксида кремния в качестве изолятора затвора используется диэлектрик с высоким κ , а поликремний заменяется металлическими затворами (например, Intel , 2009 [81] ).

Затвор отделен от канала тонким изолирующим слоем, обычно из диоксида кремния, а затем из оксинитрида кремния . Некоторые компании начали внедрять комбинацию диэлектрика с высоким κ и металлического затвора в 45-нанометровом узле.

Когда между выводом затвора и корпуса прикладывается напряжение, генерируемое электрическое поле проникает через оксид и создает инверсионный слой или канал на границе полупроводник-изолятор, из-за чего эта часть становится менее p-типа и открывает путь для проводимости. тока, что приводит к увеличению напряжения между затвором и корпусом, которое отталкивает отверстия и создает слой неподвижных носителей, заряженных отрицательно. Инверсионный слой обеспечивает канал, по которому ток может проходить между выводами истока и стока. Изменение напряжения между затвором и корпусом модулирует проводимость этого слоя и, таким образом, регулирует ток между стоком и истоком. Это называется режимом улучшения.

Операция [ править ]

Структура металл – оксид – полупроводник [ править ]

Традиционная структура металл – оксид – полупроводник (МОП) получается путем выращивания слоя диоксида кремния ( SiO

2) поверх кремниевой подложки, обычно путем термического окисления и нанесения слоя металла или поликристаллического кремния (обычно используется последний). Поскольку диоксид кремния является диэлектрическим материалом, его структура эквивалентна плоскому конденсатору , в котором один из электродов заменен полупроводником .

Когда напряжение подается на МОП-структуру, оно изменяет распределение зарядов в полупроводнике. Если мы рассмотрим полупроводник p-типа (с плотностью акцепторов , p плотность дырок; p = N A в нейтральном объеме), положительное напряжение`` от затвора к телу (см. Рисунок) создает слой обеднения , заставляя положительно заряженные дырки от границы затвор-изолятор / полупроводник, оставляя открытой свободную от носителей область неподвижных отрицательно заряженных ионов-акцепторов (см. легирование (полупроводник) ). Если он достаточно высок, в инверсионном слое образуется высокая концентрация отрицательных носителей заряда. расположен в тонком слое рядом с границей раздела между полупроводником и диэлектриком.

Обычно напряжение затвора, при котором объемная плотность электронов в инверсионном слое совпадает с объемной плотностью дырок в теле, называется пороговым напряжением . Когда напряжение между затвором транзистора и истоком ( V GS ) превышает пороговое напряжение ( V th ), разница известна как напряжение перегрузки .

Эта структура с корпусом p-типа является основой полевого МОП-транзистора n-типа, который требует добавления областей истока и стока n-типа.

МОП-конденсаторы и диаграммы полос [ править ]

В этом разделе не процитировать любые источники . ( Январь 2019 г. ) ( Узнайте, как и когда удалить этот шаблон сообщения ) |

Конструкция МОП-конденсатора является сердцем МОП-транзистора. Рассмотрим МОП-конденсатор с кремниевой базой p-типа. Если на затвор приложено положительное напряжение, отверстия, которые находятся на поверхности подложки p-типа, будут отталкиваться электрическим полем, создаваемым приложенным напряжением. Сначала дырки будут просто отталкиваться, и то, что останется на поверхности, будет неподвижными (отрицательными) атомами акцепторного типа, что создаст на поверхности область обеднения. Помните, что дырка создается акцепторным атомом, например бором, у которого на один электрон меньше, чем у кремния. Можно спросить, как можно отразить дыры, если они на самом деле не являются сущностями? Ответ заключается в том, что на самом деле происходит не то, что дырка отталкивается, а электроны притягиваются положительным полем и заполняют эти дырки,создание обедненной области, где нет носителей заряда, потому что электрон теперь закреплен на атоме и неподвижен.

По мере увеличения напряжения на затворе будет точка, в которой поверхность над обедненной областью будет преобразована из p-типа в n-тип, поскольку электроны из основной области начнут притягиваться большим электрическим полем. Это известно как инверсия . Пороговое напряжение, при котором происходит это преобразование, является одним из наиболее важных параметров полевого МОП-транзистора.

В случае объема p-типа инверсия происходит, когда собственный уровень энергии на поверхности становится меньше уровня Фермина поверхности. Это видно из ленточной диаграммы. Помните, что уровень Ферми определяет тип обсуждаемого полупроводника. Если уровень Ферми равен внутреннему уровню, полупроводник является внутренним или чистым типом. Если уровень Ферми расположен ближе к зоне проводимости (валентной зоне), то полупроводник будет иметь n-тип (p-тип). Следовательно, когда напряжение затвора увеличивается в положительном смысле (для данного примера), это «искривляет» полосу собственных энергетических уровней, так что она будет изгибаться вниз по направлению к валентной зоне. Если уровень Ферми находится ближе к валентной зоне (для p-типа), наступит момент, когда собственный уровень начнет пересекать уровень Ферми, и когда напряжение достигнет порогового напряжения, собственный уровень действительно пересечет уровень Ферми. , и это то, что называется инверсией.В этот момент поверхность полупроводника превращается из p-типа в n-тип. Помните, что, как сказано выше, если уровень Ферми лежит выше собственного уровня, полупроводник относится к n-типу, поэтому при инверсии, когда собственный уровень достигает и пересекает уровень Ферми (который находится ближе к валентной зоне), полупроводник Тип меняется на поверхности, что диктуется относительным положением уровней Ферми и собственной энергии.Тип полупроводника изменяется на поверхности в зависимости от относительного положения уровней Ферми и собственной энергии.Тип полупроводника изменяется на поверхности в зависимости от относительного положения уровней Ферми и собственной энергии.

Структура и формирование каналов [ править ]

МОП-транзистор основан на модуляции концентрации заряда за счет МОП-емкости между основным электродом и электродом затвора, расположенным над корпусом и изолированным от всех других областей устройства диэлектрическим слоем затвора . Если используются диэлектрики, отличные от оксида, устройство может называться полевым транзистором металл-диэлектрик-полупроводник (MISFET). По сравнению с МОП-конденсатором, МОП-транзистор включает в себя два дополнительных вывода ( исток и сток).), каждая из которых связана с отдельными высоколегированными областями, которые разделены областью тела. Эти области могут быть как p-, так и n-типа, но обе должны быть одного и того же типа и противоположного типа по отношению к области тела. Исток и сток (в отличие от корпуса) сильно легированы, что обозначено знаком «+» после типа легирования.

Если МОП-транзистор является n-канальным или n-МОП-транзистором, то исток и сток являются n + областями, а тело - областью p . Если полевой МОП-транзистор является p-каналом или полевым МОП-транзистором, то исток и сток являются p + областями, а тело - n областью. Источник назван так потому, что он является источником носителей заряда (электроны для n-канала, дырки для p-канала), которые текут через канал; аналогично сток - это место, где носители заряда покидают канал.

Заселенность энергетических зон в полупроводнике определяется положением уровня Ферми относительно краев энергетических зон полупроводника.

При достаточном напряжении на затворе край валентной зоны отодвигается от уровня Ферми, а дырки от тела отводятся от затвора.

При еще большем смещении затвора вблизи поверхности полупроводника край зоны проводимости приближается к уровню Ферми, заполняя поверхность электронами в инверсионном слое или n-канале на границе раздела между p-областью и оксидом. Этот проводящий канал проходит между истоком и стоком, и ток проходит через него, когда между двумя электродами прикладывается напряжение. Увеличение напряжения на затворе приводит к более высокой плотности электронов в инверсионном слое и, следовательно, увеличивает ток между истоком и стоком. Для напряжений на затворе ниже порогового значения канал заполняется слабо, и между истоком и стоком может протекать только очень небольшой подпороговый ток утечки.

Когда прикладывается отрицательное напряжение затвор-исток, он создает p-канал на поверхности n-области, аналогично случаю n-канала, но с противоположными полярностями зарядов и напряжений. Когда напряжение менее отрицательное, чем пороговое значение (отрицательное напряжение для p-канала) применяется между затвором и истоком, канал исчезает, и только очень небольшой подпороговый ток может течь между истоком и стоком. Устройство может содержать кремний на изоляторе.устройство, в котором скрытый оксид образуется под тонким слоем полупроводника. Если область канала между диэлектриком затвора и скрытой оксидной областью очень тонкая, канал упоминается как сверхтонкая область канала с областями истока и стока, сформированными с обеих сторон в тонком полупроводниковом слое или над ним. Могут использоваться другие полупроводниковые материалы. Когда области истока и стока сформированы над каналом полностью или частично, они называются приподнятыми областями истока / стока.

| Параметр | nMOSFET | pMOSFET | |

|---|---|---|---|

| Тип источника / стока | n-тип | р-тип | |

| Тип канала (МОП-конденсатор) | n-тип | р-тип | |

Тип ворот | Поликремний | п + | р + |

| Металл | φ m ~ Si зона проводимости | φ m ~ Si валентная зона | |

| Тип колодца | р-тип | n-тип | |

| Пороговое напряжение, В th |

|

| |

| Гибка ленты | Вниз | Снизу вверх | |

| Носители инверсионного слоя | Электроны | Отверстия | |

| Тип субстрата | р-тип | n-тип | |

Режимы работы [ править ]

вверху слева: подпороговый, вверху справа: омический режим, внизу слева: активный режим в начале защемления, внизу справа: активный режим в самом начале защемления - модуляция длины канала очевидна

Работа полевого МОП-транзистора может быть разделена на три различных режима в зависимости от напряжений на клеммах. В следующем обсуждении используется упрощенная алгебраическая модель. [84] Характеристики современных полевых МОП-транзисторов сложнее, чем представленная здесь алгебраическая модель. [85]

Для n-канального полевого МОП-транзистора в режиме улучшения доступны три рабочих режима:

- Отсечка, подпороговый режим и режим слабой инверсии

Когда V GS < V th :

где - смещение затвор-исток, а - пороговое напряжение устройства.

Согласно базовой пороговой модели транзистор выключен, и между стоком и истоком нет проводимости. Более точная модель учитывает влияние тепловой энергии на распределение Ферми – Дирака по энергиям электронов, что позволяет некоторым из более энергичных электронов в источнике входить в канал и течь в сток. Это приводит к подпороговому току, который является экспоненциальной функцией напряжения затвор-исток. В то время как ток между стоком и истоком в идеале должен быть равен нулю, когда транзистор используется в качестве выключателя, существует слабый ток инверсии, иногда называемый подпороговой утечкой.

В слабой инверсии, когда источник привязан к объему, ток изменяется экспоненциально, как приблизительно определяется следующим образом: [86] [87]

где = ток при , тепловое напряжение и коэффициент наклона n определяются по формуле:

с = емкость обедненного слоя и = емкость оксидного слоя. Обычно используется это уравнение, но оно является лишь адекватным приближением для источника, привязанного к балке. Для источника, не привязанного к объему, подпороговое уравнение для тока стока при насыщении имеет вид [88] [89]

где - делитель канала, который определяется по формуле:

с = емкость обедненного слоя и = емкость оксидного слоя. В устройстве с длинным каналом отсутствует однократная зависимость тока от напряжения стока , но по мере уменьшения длины канала уменьшение барьера, вызванного стоком, приводит к зависимости напряжения стока, которая сложным образом зависит от геометрии устройства (например, легирование канала , легирование перехода и т. д.). Часто пороговое напряжение V th для этого режима определяется как напряжение затвора, при котором возникает выбранное значение тока I D0 , например, I D0 = 1 мкА, которое может отличаться от V th. -значение, используемое в уравнениях для следующих режимов.

Некоторые аналоговые схемы микромощностей предназначены для использования преимущества подпороговой проводимости. [90] [91] [92] Работая в области слабой инверсии, полевые МОП-транзисторы в этих схемах обеспечивают максимально возможное отношение крутизны к току, а именно: почти такое же, как у биполярного транзистора. [93]

Подпороговая ВАХ экспоненциально зависит от порогового напряжения, внося сильную зависимость от любых производственных изменений, которые влияют на пороговое напряжение; например: изменения толщины оксида, глубины перехода или легирования тела, которые изменяют степень снижения барьера, вызванного стоком. Возникающая в результате чувствительность к производственным изменениям усложняет оптимизацию утечек и производительности. [94] [95]

- Триодный режим или линейная область (также известный как омический режим [96] [97] )

Когда V GS > V th и V DS < V GS - V th :

Транзистор включается, и создается канал, пропускающий ток между стоком и истоком. МОП-транзистор работает как резистор, управляемый напряжением затвора относительно напряжений истока и стока. Ток от стока к истоку моделируется следующим образом:

где это носители заряда эффективной подвижность, ширина ворот, длина затвора и является ворота оксида емкости на единицу площади. Переход от экспоненциальной подпороговой области к триодной области не такой резкий, как предполагают уравнения.

- Насыщенность или активный режим [98] [99]

Когда V GS > V th и V DS ≥ (V GS - V th ):

Переключатель включен, и был создан канал, который пропускает ток между стоком и истоком. Поскольку напряжение стока выше, чем напряжение истока, электроны распространяются, и проводимость осуществляется не через узкий канал, а через более широкое, двумерное или трехмерное распределение тока, простирающееся от границы раздела и глубже в подложку. Начало этой области также известно как отсечение, чтобы указать на отсутствие области канала около стока. Хотя канал не распространяется на всю длину устройства, электрическое поле между стоком и каналом очень велико, и проводимость сохраняется. Ток стока теперь слабо зависит от напряжения стока и регулируется в основном напряжением затвор-исток и моделируется примерно как:

Дополнительный фактор, включающий λ, параметр модуляции длины канала, моделирует зависимость тока от напряжения стока из-за модуляции длины канала , что фактически аналогично эффекту Раннего, наблюдаемому в биполярных устройствах. Согласно этому уравнению, ключевым параметром конструкции крутизна полевого МОП-транзистора является:

где комбинация V ov = V GS - V th называется напряжением перегрузки , [100] и где V DSsat = V GS - V th учитывает небольшую неоднородность, которая в противном случае возникла бы при переходе между триодом и областью насыщения.

Другим ключевым параметром конструкции является выходное сопротивление полевого МОП-транзистора, определяемое как

- .

r out - это величина, обратная g DS, где . I D - это выражение в области насыщения.

Если принять λ равным нулю, результирующее бесконечное выходное сопротивление может упростить анализ схемы, однако это может привести к нереалистичным прогнозам схемы, особенно в аналоговых схемах.

Поскольку длина канала становится очень короткой, эти уравнения становятся неточными. Возникают новые физические эффекты. Например, перенос носителей в активном режиме может быть ограничен насыщением скорости . Когда преобладает насыщение по скорости, ток стока насыщения более близок к линейному, чем к квадратичному по V GS . На еще меньших длинах носители транспортируются с почти нулевым рассеянием, известным как квазибаллистический транспорт . В баллистическом режиме носители движутся со скоростью инжекции, которая может превышать скорость насыщения и приближается к скорости Ферми.при высокой плотности инверсионного заряда. Кроме того, снижение барьера, вызванного стоком, увеличивает ток отключения (отсечки) и требует увеличения порогового напряжения для компенсации, что, в свою очередь, снижает ток насыщения.

Эффект тела [ править ]

Заселенность энергетических зон в полупроводнике определяется положением уровня Ферми относительно краев энергетических зон полупроводника. Применение обратного смещения источник-подложка pn-перехода источник-тело вводит расщепление между уровнями Ферми для электронов и дырок, сдвигая уровень Ферми для канала дальше от края зоны, уменьшая заполненность канала. Эффект заключается в увеличении напряжения затвора, необходимого для установления канала, как показано на рисунке. Это изменение силы канала за счет применения обратного смещения называется «эффектом тела».

Проще говоря, используя пример nMOS, смещение затвор-тело V GB позиционирует энергетические уровни зоны проводимости, в то время как смещение источник-тело V SB размещает уровень Ферми электронов вблизи границы раздела, определяя занятость этих уровней вблизи интерфейс и, следовательно, сила инверсионного слоя или канала.

Влияние тела на канал можно описать с помощью модификации порогового напряжения, аппроксимируемого следующим уравнением:

- VTB = VT0, если VSB = 0, т. Е. Пороговое напряжение для замыкания клемм затвора и корпуса.

где V TB - это пороговое напряжение при наличии смещения подложки, V T0 - нулевое значение V SB порогового напряжения, - параметр эффекта тела, а 2 φ B - приблизительное падение потенциала между поверхностью и объемом на обедненном слое, когда V SB = 0 и смещения затвора достаточно, чтобы гарантировать наличие канала. [101] Как показывает это уравнение, обратное смещение V SB > 0 вызывает увеличение порогового напряжения V TB и, следовательно, требует большего напряжения затвора перед заполнением канала.

Тело может использоваться как вторые ворота, и иногда их называют «задними воротами»; Эффект тела иногда называют «эффектом заднего прохода». [102]

Обозначения схем [ править ]

Для полевого МОП-транзистора используются различные символы. Базовая конструкция обычно представляет собой линию для канала с истоком и стоком, оставляя его под прямым углом, а затем изгибаясь под прямым углом в том же направлении, что и канал. Иногда три линейных сегмента используются для режима улучшения и сплошная линия для режима истощения (см. Режимы истощения и улучшения ). Еще одна линия проводится параллельно каналу для ворот.

Основная часть или тело соединение, если показана, показано соединенный с задней стороной канала со стрелкой , указывающей PMOS или NMOS. Стрелки всегда указывают от P к N, поэтому NMOS (N-канал в P-лунке или P-субстрате) имеет стрелку, указывающую внутрь (от объема к каналу). Если основная часть подключена к источнику (как это обычно бывает с дискретными устройствами), она иногда наклоняется, чтобы встретиться с источником, выходящим из транзистора. Если основная часть не показана (как это часто бывает в конструкции ИС, поскольку они обычно являются общей массой), иногда используется символ инверсии для обозначения PMOS, в качестве альтернативы стрелка на источнике может использоваться таким же образом, как для биполярных транзисторов ( выход для nMOS, вход для pMOS).

Сравнение символов MOSFET режима улучшения и режима истощения, а также символов JFET . Ориентация символов (наиболее важно положение истока относительно стока) такова, что более положительные напряжения появляются выше на странице, чем менее положительные напряжения, подразумевая, что ток течет «вниз» по странице: [103] [104] [105 ]

| P-канал | |||||

|---|---|---|---|---|---|

| N-канал | |||||

| JFET | MOSFET enh. | MOSFET enh. (без пачки) | MOSFET Зав. | ||

На схемах, где G, S, D не обозначены, подробные характеристики символа указывают, какой терминал является истоком, а какой сток. Для символов MOSFET режима улучшения и режима истощения (во втором и пятом столбцах) терминал источника - это тот, который соединен со стрелкой. Кроме того, на этой диаграмме ворота показаны в форме буквы «L», входная ветвь которой ближе к S, чем к D, что также указывает на то, что есть что. Однако эти символы часто рисуются с Т-образным затвором (как и везде на этой странице), поэтому для обозначения терминала источника следует полагаться именно на наконечник стрелки.

Для символов, на которых изображен стержень или корпус, клемма, здесь показана внутренняя связь с источником (т. Е. Черная стрелка на диаграммах в столбцах 2 и 5). Это типичная конфигурация, но отнюдь не единственная важная конфигурация. В общем, полевой МОП-транзистор представляет собой четырехполюсное устройство, и в интегральных схемах многие из полевых МОП-транзисторов имеют общее соединение корпуса, не обязательно подключенное к клеммам истока всех транзисторов.

Типы полевых МОП-транзисторов [ править ]

Логика PMOS и NMOS [ править ]

Логика P-канала MOS (PMOS) использует полевые МОП - транзисторы с p-каналом для реализации логических вентилей и других цифровых схем . Логика N-канального MOS (NMOS) использует n-канальные MOSFET для реализации логических вентилей и других цифровых схем.

Для устройств с равным током возбуждения полевые МОП-транзисторы с n-каналом могут быть меньше, чем полевые МОП-транзисторы с p-каналом, поскольку носители заряда ( дырки ) с p-каналом имеют меньшую подвижность, чем носители заряда с n-каналом ( электроны ), и производят только один Тип MOSFET на кремниевой подложке дешевле и технически проще. Это были руководящие принципы при разработке логики NMOS, в которой используются исключительно n-канальные полевые МОП-транзисторы. Однако, в отличие от логики CMOS (без учета тока утечки ), логика NMOS потребляет энергию, даже если переключение не происходит.

Мохамед Аталла и Давон Канг первоначально продемонстрировали устройства pMOS и nMOS с длиной затвора 20 мкм, а затем 10 мкм в 1960 году. [15] [106] Их оригинальные устройства MOSFET также имели толщину оксида затвора 100 нм . [107] Однако устройства nMOS были непрактичными, и только устройства типа pMOS были практическими рабочими устройствами. [15] Несколько лет спустя был разработан более практичный процесс NMOS. Первоначально NMOS была быстрее, чем CMOS , поэтому в 1970-х годах NMOS более широко использовалась в компьютерах. [108] С развитием технологий логика CMOS вытеснила логику NMOS в середине 1980-х годов и стала предпочтительным процессом для цифровых микросхем.

Дополнительная МОП (CMOS) [ править ]

MOSFET используется в цифровой комплементарной логике металл-оксид-полупроводник ( CMOS ) [109], которая использует p- и n-канальные MOSFET в качестве строительных блоков. Перегрев является серьезной проблемой в интегральных схемах, поскольку все больше транзисторов упаковывается во все более мелкие микросхемы. Логика CMOS снижает энергопотребление, поскольку ток не течет (в идеале) и, следовательно, не потребляется никакая мощность , за исключением случаев, когда входы на логические элементыпереключаются. CMOS выполняет это снижение тока, дополняя каждый nMOSFET полевым pMOSFET и соединяя оба затвора и оба стока вместе. Высокое напряжение на затворах заставит nMOSFET проводить, а pMOSFET - не проводить, а низкое напряжение на затворах вызывает обратное. Во время переключения, когда напряжение переходит из одного состояния в другое, оба полевых МОП-транзистора будут работать на короткое время. Такое расположение значительно снижает потребление энергии и тепловыделение.

CMOS была разработана Chih-Tang Sah и Frank Wanlass в Fairchild Semiconductor в 1963 году. [32] CMOS потребляла меньше энергии, но изначально была медленнее, чем NMOS, которая более широко использовалась для компьютеров в 1970-х годах. В 1978 году Hitachi представила технологию CMOS с двумя лунками, которая позволила CMOS достичь производительности NMOS с меньшим энергопотреблением. Процесс двухъямной CMOS в конечном итоге обогнал NMOS как наиболее распространенный процесс производства полупроводников для компьютеров в 1980-х годах. [108] К 1970-1980-м годам логика CMOS потребляла в 7 раз меньше энергии, чем логика NMOS, [108]и примерно в 100000 раз меньше мощности, чем биполярная транзисторно-транзисторная логика (TTL). [110]

Режим истощения [ править ]

Существуют полевые МОП - транзисторы с режимом истощения , которые используются реже, чем уже описанные стандартные устройства с расширенным режимом . Это полевые МОП-транзисторы, которые легированы таким образом, что канал существует даже при нулевом напряжении от затвора до истока. Для управления каналом к затвору прикладывается отрицательное напряжение (для n-канального устройства), истощая канал, что уменьшает ток, протекающий через устройство. По сути, устройство режима истощения эквивалентно нормально замкнутому (включенному) переключателю, в то время как устройство расширенного режима эквивалентно нормально разомкнутому (выключенному) переключателю. [111]

Из-за низкого коэффициента шума в РЧ- диапазоне и лучшего усиления эти устройства часто предпочитают биполярным входам в РЧ-интерфейсах, например, в телевизорах .

Истощение режима MOSFET семейства включают BF960 по Siemens и Telefunken , и BF980 в 1980 году Philips (впоследствии NXP полупроводники ), производные которых все еще используются в АРУ и РЧ смесителя передних-концов.

Полевой транзистор металл – изолятор – полупроводник (MISFET) [ править ]

Полевой транзистор металл – изолятор – полупроводник [112] [113] [114] или MISFET - это более общий термин, чем MOSFET, и синоним полевого транзистора с изолированным затвором (IGFET). Все МОП-транзисторы являются МОП-транзисторами, но не все МОП-транзисторы являются МОП-транзисторами.

Диэлектрическим изолятором затвора в MISFET является диоксид кремния в MOSFET, но можно использовать и другие материалы. Диэлектрика затвора находится непосредственно ниже электрода затвора и над каналом на МДП - транзистора. Термин « металл» исторически используется для материала затвора, хотя сейчас это обычно высоколегированный поликремний или какой-либо другой неметалл .

Типы изоляторов могут быть:

- Диоксид кремния в полевых МОП-транзисторах

- Органические изоляторы (например, нелегированный транс- полиацетилен ; цианоэтил пуллулан , CEP [115] ) для полевых транзисторов на органической основе. [114]

МОП-транзистор с плавающим затвором (FGMOS) [ править ]

С плавающей затвора МОП - транзистора (FGMOS) представляет собой тип полевого МОП - транзистора , где затвор электрически изолированы, создавая плавающий узел в DC и ряд вторичных ворот или входов осаждаются над плавающим затвором (FG) и электрически изолированы от него. Первый отчет о MOSFET с плавающим затвором (FGMOS) был сделан Давоном Кангом (соавтором оригинального MOSFET) и Саймоном Мин Сзе в 1967 году. [116]

FGMOS обычно используется в качестве ячейки памяти с плавающим затвором , цифрового запоминающего элемента в EPROM , EEPROM и флэш-памяти . Другие применения FGMOS включают нейронный вычислительный элемент в нейронных сетях , аналоговый запоминающий элемент, цифровые потенциометры и однотранзисторные ЦАП .

Power MOSFET [ править ]

Силовые полевые МОП-транзисторы имеют другую структуру. [117] Как и у большинства силовых устройств, конструкция вертикальная, а не плоская. Используя вертикальную структуру, транзистор может выдерживать как высокое напряжение блокировки, так и большой ток. Номинальное напряжение транзистора является функцией легирования и толщины N- эпитаксиального слоя.слой (см. поперечное сечение), в то время как текущий рейтинг является функцией ширины канала (чем шире канал, тем выше ток). В планарной структуре номинальный ток и напряжение пробоя являются функцией размеров канала (соответственно ширины и длины канала), что приводит к неэффективному использованию «кремниевого комплекса». При вертикальной структуре площадь компонента примерно пропорциональна току, который он может выдерживать, а толщина компонента (фактически толщина N-эпитаксиального слоя) пропорциональна напряжению пробоя. [118]

Полевые МОП-транзисторы с боковой структурой в основном используются в высококачественных аудиоусилителях и мощных акустических системах. Их преимущество - лучшее поведение в насыщенной области (соответствующей линейной области биполярного транзистора ), чем у вертикальных полевых МОП-транзисторов. Вертикальные полевые МОП-транзисторы предназначены для коммутации приложений. [119]

Силовой полевой МОП-транзистор, который обычно используется в силовой электронике , был разработан в начале 1970-х годов. [120] Мощный полевой МОП-транзистор обеспечивает низкую мощность привода затвора, высокую скорость переключения и расширенные возможности параллельного подключения. [4]

Двойной диффузионный металл – оксид – полупроводник (DMOS) [ править ]

Существуют VDMOS (вертикальный металлооксидный полупроводник с двойной диффузией ) и LDMOS (боковой металлооксидный полупроводник с двойной диффузией ). Большинство мощных полевых МОП-транзисторов изготавливаются с использованием этой технологии.

МОП-конденсатор [ править ]

Конденсатор MOS является частью структуры MOSFET, где конденсатор MOS окружен двумя pn переходами . [121] МОП-конденсатор широко используется в качестве накопительного конденсатора в микросхемах памяти и в качестве основного строительного блока устройства с зарядовой связью (ПЗС) в технологии датчиков изображения . [122] В DRAM (динамической памяти с произвольным доступом ) каждая ячейка памяти обычно состоит из полевого МОП-транзистора и МОП-конденсатора. [123]

Тонкопленочный транзистор (TFT) [ править ]

Тонкопленочный транзистор (TFT) , представляет собой тип полевого МОП - транзистора отличается от стандартного объемного МОП - транзистора. [124] Первый TFT был изобретен Полом К. Веймером в RCA в 1962 году, основываясь на более ранней работе Аталлы и Канга по полевым МОП-транзисторам. [125]

Идея жидкокристаллического дисплея (LCD) на основе TFT была придумана Бернардом Лехнером из RCA Laboratories в 1968 году. [126] Лехнер, Ф. Дж. Марлоу, Э. О. Нестер и Дж. Талтс продемонстрировали концепцию в 1968 году с помощью матричного динамического рассеяния 18x2. ЖК-дисплей, в котором использовались стандартные дискретные полевые МОП-транзисторы, поскольку в то время производительность TFT была недостаточной. [127]

Биполярно-МОП транзисторы [ править ]

BiCMOS - это интегральная схема , объединяющая транзисторы BJT и CMOS на одном кристалле. [128]

Биполярный транзистор с изолированным затвором (IGBT) представляет собой мощный транзистор с характеристиками как на МОП - транзистора и биполярный плоскостной транзистор (BJT). [129]

Датчики MOS [ править ]

Был разработан ряд датчиков MOSFET для измерения физических , химических , биологических параметров и параметров окружающей среды . [130] Наиболее ранние датчики MOSFET включают открытый затвор полевого транзистора (OGFET) , введенный Johannessen в 1970 году, [130] ион-чувствительный полевой транзистор (ИСПТ) , изобретенный Пита Bergveld в 1970 году, [131] на адсорбционную FET ( ADFET), запатентованный PF Cox в 1974 году, и чувствительный к водороду MOSFET, продемонстрированный И. Лундстромом, М.С. Шивараманом, С.С. Свенсоном и Л. Лундквистом в 1975 году.[130] ISFET - это особый тип полевого МОП-транзистора с затвором на определенном расстоянии [130], в котором металлический затвор заменен ионно- чувствительной мембраной ,раствором электролита и электродом сравнения . [132]

К середине 1980-х годов было разработано множество других датчиков MOSFET, включая полевой транзистор газового датчика (GASFET), полевой транзистор с поверхностным доступом (SAFET), транзистор потока заряда (CFT), датчик давления FET (PRESSFET), химический полевой транзистор ( ChemFET), эталонный ISFET (REFET), биосенсорный полевой транзистор (BioFET), ферментно-модифицированный полевой транзистор (ENFET) и иммунологически модифицированный полевой транзистор (IMFET). [130] В начале 2000 - х лет, типы BioFET , такие как ДНК - полевой транзистор (DNAFET), ген-модифицированный полевые транзисторы (GenFET) и клеточный потенциал были разработаны BioFET (CPFET). [132]

В технологии цифровых изображений используются два основных типа датчиков изображения : устройство с зарядовой связью (ПЗС) и датчик с активными пикселями (датчик КМОП). И ПЗС, и КМОП-сенсоры основаны на технологии МОП, при этом ПЗС-матрица основана на МОП-конденсаторах, а КМОП-сенсор - на МОП-транзисторах. [77]

Полевой транзистор с несколькими затворами (MuGFET) [ править ]

Двойной затвор МОП - транзистор ( два правительства) имеет Тетрод конфигурацию, в которой оба воротах контролировать ток в устройстве. Он обычно используется для малосигнальных устройств в радиочастотных приложениях, где смещение затвора на стороне стока при постоянном потенциале снижает потери усиления, вызванные эффектом Миллера , заменяя два отдельных транзистора в каскодной конфигурации. Другие распространенные применения в радиочастотных схемах включают регулировку усиления и смешение (преобразование частоты). Описание тетрода , хотя и точное, не повторяет тетрод на электронных лампах. Тетроды на электронных лампах, в которых используется экранная сетка, демонстрируют гораздо более низкую емкость сетки и гораздо более высокие выходное сопротивление и коэффициент усиления по напряжению, чем триодные вакуумные лампы.. Эти улучшения обычно на порядок (в 10 раз) или значительно больше. Тетродные транзисторы (будь то биполярные переходные или полевые) не демонстрируют таких значительных улучшений.

FinFET является двойным затвором кремния на изоляторе устройство, один из множества геометрических форм вводятся для уменьшения влияния коротких каналов и уменьшить сток-индуцированный барьер опускания. Плавника относится к узкому каналу между истоком и стоком. Тонкий изолирующий оксидный слой с обеих сторон ребра отделяет его от затвора. КНИТЕ FinFETs с толстым оксидом на верхней части ребер называется двойным затвором , и те , с тонким оксидом на вершине, а также по бокам называются тройным затвор FinFETs. [133] [134]

С двойным затвором полевой МОП - транзистор был впервые продемонстрирован в 1984 году электротехнической лаборатории исследователей Тосихиро Sekigawa и Yutaka Hayashi. [135] [136] GAAFET (затвор-все вокруг полевого МОП - транзистора), тип мульти-затвора неплоской 3D транзистора , была впервые продемонстрирована в 1988 году Toshiba исследовательской группы , включая Фьюджио Масуока , Х. Takato и К. Sunouchi . [137] [138] FinFET (плавник полевой транзистор), тип 3D неплоской двойным затвором полевого МОП - транзистора, возникла из исследования DIGH Hisamoto и его командой в Центральной научно - исследовательской лаборатории Hitachiв 1989 году. [139] [140] Разработка многозатворных полевых МОП-транзисторов на основе нанопроволок с тех пор стала фундаментальной для наноэлектроники . [141]

Квантовый полевой транзистор (QFET) [ править ]

Квантовой полевой транзистор (QFET) или квантовой ямы полевой транзистор (QWFET) представляет собой тип полевого МОП - транзистора [142] [143] [144] , что имеет преимущество квантового туннелирования , чтобы значительно увеличить скорость работы транзистора. [145]

Радиационно-стойкая-конструктивная (RHBD) [ править ]

Полупроводниковые электронные схемы субмикрометрового и нанометрового размеров являются первоочередной задачей для работы в пределах нормальных допусков в суровых радиационных средах, таких как космическое пространство . Один из конструктивных подходов к изготовлению радиационно-стойких конструкций.(RHBD) устройство на закрытых транзисторах (ELT). Обычно затвор полевого МОП-транзистора окружает сток, расположенный в центре ELT. Источник полевого МОП-транзистора окружает затвор. Другой RHBD MOSFET называется H-Gate. Оба этих транзистора имеют очень низкий ток утечки по отношению к излучению. Однако они имеют большие размеры и занимают больше места на кремнии, чем стандартный полевой МОП-транзистор. В более старых конструкциях STI (изоляция из неглубоких канавок) радиационные удары вблизи области оксида кремния вызывают инверсию каналов в углах стандартного полевого МОП-транзистора из-за накопления радиационно-индуцированных захваченных зарядов. Если заряды достаточно велики, накопленные заряды воздействуют на края поверхности STI вдоль канала около интерфейса канала (затвора) стандартного полевого МОП-транзистора.Таким образом, инверсия канала устройства происходит по краям канала, и устройство создает путь утечки в закрытом состоянии, вызывая включение устройства. Таким образом, надежность цепей сильно ухудшается. ELT предлагает множество преимуществ. Эти преимущества включают улучшениенадежность за счет уменьшения нежелательной инверсии поверхности на краях затвора, которая возникает в стандартном полевом МОП-транзисторе. Поскольку края затвора заключены в ELT, нет края оксида затвора (STI на интерфейсе затвора), и, таким образом, утечка в закрытом состоянии транзистора значительно снижается. Микроэлектронные схемы малой мощности, включая компьютеры, устройства связи и системы мониторинга в космических челноках и спутниках, сильно отличаются от того, что используется на Земле. Они требуют излучения (высокоскоростные атомные частицы, такие как протон и нейтрон , рассеивание магнитной энергии солнечной вспышки в космическом пространстве Земли, энергетические космические лучи, такие как рентгеновские лучи , гамма-лучи.и т. д.) толерантные схемы. Эта специальная электроника разработана с применением различных методов с использованием полевых МОП-транзисторов с RHBD для обеспечения более безопасных путешествий и выходов в открытый космос для космонавтов.

Приложения [ править ]

МОП - транзистор обычно образует основу современной электроники , [42] в качестве доминирующего транзистора в цифровых схемах , а также аналоговых интегральных схем . [3] Это основа для множества современных технологий, [146] и обычно используется для широкого круга приложений. [47] Согласно Жан-Пьеру Колинджу, многие современные технологии не существовали бы без MOSFET, например, современная компьютерная промышленность , цифровые телекоммуникационные системы, видеоигры , карманные калькуляторы и цифровые наручные часы . [146]

Дискретные полевые МОП-транзисторы широко используются в таких приложениях, как импульсные источники питания , частотно-регулируемые приводы и другие приложения силовой электроники, где каждое устройство может переключать тысячи ватт. Радиочастотные усилители вплоть до диапазона УВЧ используют полевые МОП-транзисторы в качестве аналоговых сигналов и усилителей мощности. Радиосистемы также используют полевые МОП-транзисторы в качестве генераторов или смесителей для преобразования частот. Устройства MOSFET также применяются в усилителях мощности звуковой частоты для систем оповещения, звукоусиления, домашних и автомобильных звуковых систем. [ необходима цитата ]

МОП-транзисторы в интегральных схемах являются основными элементами компьютерных процессоров , полупроводниковой памяти , датчиков изображения и большинства других типов интегральных схем.

MOS интегральная схема (MOS IC) [ править ]

MOSFET - это наиболее широко используемый тип транзистора и наиболее важный компонент устройства в микросхемах (ИС). [147] монолитной интегральной схемы чип был включен по пассивации поверхности процесса, который электрически стабилизированной кремниевых поверхностей с помощью термического окисления , что делает возможным изготовить монолитные интегральные микросхемы схемы с использованием кремния. Процесс поверхностной пассивации был разработан Мохамедом М. Аталлой в Bell Labs в 1957 году. Это было основой для планарного процесса , разработанного Джин Хорни вFairchild Semiconductor в начале 1959 года, что сыграло решающую роль в изобретении монолитной интегральной схемы Робертом Нойсом позже в 1959 году. [148] [149] [17] В том же году [8] Аталла использовал свой процесс пассивации поверхности для изобретения MOSFET с Давоном Кангом в Bell Labs. [14] [13] За этим последовало развитие чистых помещений для снижения загрязнения до уровней, которые ранее никогда не считались необходимыми, и совпало с развитием фотолитографии [150], которая, наряду с пассивацией поверхности и планарным процессом, позволила схемам быть сделано в несколько шагов.

Мохамед Аталла впервые предложил концепцию микросхемы МОП-интегральной схемы (МОП-ИС) в 1960 году, отметив, что простота изготовления МОП-транзистора сделала его полезным для интегральных схем. [9] В отличие от биполярных транзисторов, которые требовали ряда шагов для изоляции p – n перехода транзисторов на кристалле, полевые МОП-транзисторы не требовали таких шагов, но их можно было легко изолировать друг от друга. [29] Его преимущество для интегральных схем было повторно итерация по Давону Канга в 1961 г. [21] Si - SiO 2Система обладала техническими достоинствами: низкой стоимостью производства (в расчете на схему) и простотой интеграции. Эти два фактора, наряду с его быстро масштабируемой миниатюризацией и низким потреблением энергии , привели к тому, что MOSFET стал наиболее широко используемым типом транзисторов в микросхемах IC.

Самой ранней экспериментальной МОП ИС, которая была продемонстрирована, была микросхема с 16 транзисторами, построенная Фредом Хейманом и Стивеном Хофштейном на RCA в 1962 году. [56] General Microelectronics позже представила первые коммерческие МОП интегральные схемы в 1964 году, состоящие из 120 p-канальных транзисторов. [151] Это был 20-битный регистр сдвига , разработанный Робертом Норманом [56] и Фрэнком Ванлассом . [152] В 1968 году исследователи Fairchild Semiconductor Федерико Фаггин и Том Кляйн разработали первую МОП-микросхему с кремниевым затвором . [35]

MOS крупномасштабная интеграция (MOS LSI) [ править ]

Благодаря высокой масштабируемостью , [48] и гораздо более низкое энергопотреблением и более высокой плотностью , чем биполярные транзисторы, [51] МОП - транзистор сделал возможное создание высокой плотности интегральных микросхем. [1] К 1964 году MOS-чипы достигли более высокой плотности транзисторов и более низких производственных затрат, чем биполярные чипы. Микросхемы МОП усложнялись со скоростью, предсказываемой законом Мура , что привело к крупномасштабной интеграции (БИС) с сотнями полевых МОП-транзисторов на кристалле к концу 1960-х годов. [153] Технология MOS позволила к началу 1970-х годов интегрировать более 10 000 транзисторов на одном кристалле LSI.[154] перед тем, как позже разрешить очень крупномасштабную интеграцию (СБИС). [50] [155]

Микропроцессоры [ править ]

МОП - транзистор является основой каждого микропроцессора , [45] и был ответственен за изобретение микропроцессора. [156] Истоки как микропроцессора, так и микроконтроллера можно проследить до изобретения и развития технологии МОП. Применение микросхем MOS LSI в вычислениях послужило основой для первых микропроцессоров, поскольку инженеры начали осознавать, что полный компьютерный процессор может содержаться в одном кристалле MOS LSI. [153]

Самые ранние микропроцессоры были полностью MOS-микросхемами, построенными на схемах MOS LSI. Первые многочиповые микропроцессоры, Four-Phase Systems AL1 в 1969 году и Garrett AiResearch MP944 в 1970 году, были разработаны с использованием нескольких микросхем MOS LSI. Первый коммерческий однокристальный микропроцессор, Intel 4004 , был разработан Федерико Фаггин с использованием его технологии МОП-микросхемы с кремниевым затвором, совместно с инженерами Intel Марцианом Хоффом и Стэном Мазором , а также инженером Busicom Масатоши Шима . [157] С появлением CMOSМикропроцессоры В 1975 году термин «микропроцессоры MOS» стал обозначать микросхемы, полностью изготовленные из логики PMOS или полностью изготовленные из логики NMOS , в отличие от «микропроцессоров CMOS» и «биполярных процессоров с срезами бит ». [158]

Схемы CMOS [ править ]

Цифровой [ править ]

Развитие цифровых технологий, таких как микропроцессоры , послужило стимулом для развития технологии MOSFET быстрее, чем любой другой тип кремниевых транзисторов. [159] Большим преимуществом полевых МОП-транзисторов для цифровой коммутации является то, что оксидный слой между затвором и каналом предотвращает протекание постоянного тока через затвор, дополнительно снижая потребляемую мощность и обеспечивая очень большой входной импеданс. Изолирующий оксид между затвором и каналом эффективно изолирует MOSFET в одном логическом каскаде от более ранних и более поздних каскадов, что позволяет одному выходу MOSFET управлять значительным количеством входов MOSFET. Логика на основе биполярных транзисторов (например, TTL) не имеет такой большой емкости разветвления. Эта изоляция также позволяет разработчикам в некоторой степени независимо игнорировать эффекты нагрузки между этапами логики. Эта степень определяется рабочей частотой: по мере увеличения частоты входное сопротивление полевых МОП-транзисторов уменьшается.

Аналог [ править ]

Преимущества полевого МОП-транзистора в цифровых схемах не выражаются в превосходстве во всех аналоговых схемах . Эти два типа схем основаны на различных особенностях поведения транзисторов. Цифровые схемы переключаются, проводя большую часть своего времени либо полностью включенными, либо полностью выключенными. Переход от одного к другому касается только скорости и требуемой зарядки. Аналоговые схемы зависят от работы в переходной области, где небольшие изменения V gs могут модулировать выходной (сток) ток. JFET и биполярный переходной транзистор (BJT) предпочтительны для точного согласования (соседних устройств в интегральных схемах), более высокой крутизныи определенные температурные характеристики, которые упрощают сохранение прогнозируемой производительности при изменении температуры контура.

Тем не менее, полевые МОП-транзисторы широко используются во многих типах аналоговых схем из-за их собственных преимуществ (нулевой ток затвора, высокий и регулируемый выходной импеданс и повышенная надежность по сравнению с биполярными транзисторами, которые могут быть необратимо ухудшены даже при небольшом разрушении базы эмиттера). [ расплывчато ] Характеристики и производительность многих аналоговых схем можно увеличивать или уменьшать, изменяя размеры (длину и ширину) используемых полевых МОП-транзисторов. Для сравнения, в биполярных транзисторах размер устройства существенно не влияет на его производительность. [ необходима цитата ] Идеальные характеристики полевых МОП-транзисторов относительно тока затвора (ноль) и напряжения смещения сток-исток (ноль) также делают их почти идеальными переключающими элементами, а также делаюткоммутируемые конденсаторные аналоговые схемы практичны. В своей линейной области полевые МОП-транзисторы могут использоваться в качестве прецизионных резисторов, которые могут иметь гораздо более высокое контролируемое сопротивление, чем биполярные транзисторы. В схемах большой мощности MOSFET иногда имеют то преимущество, что не страдают от теплового разгона, как BJT. [ сомнительно ] Кроме того, полевые МОП-транзисторы могут быть сконфигурированы для работы в качестве конденсаторов и цепей гиратора.которые позволяют операционным усилителям, сделанным из них, выступать в качестве катушек индуктивности, тем самым позволяя полностью построить все обычные аналоговые устройства на кристалле (за исключением диодов, которые в любом случае могут быть меньше, чем MOSFET). Это означает, что полные аналоговые схемы могут быть изготовлены на кремниевом кристалле в гораздо меньшем пространстве и с использованием более простых технологий изготовления. МОП-транзисторы идеально подходят для переключения индуктивных нагрузок из-за устойчивости к индуктивной отдаче.

Некоторые ИС объединяют аналоговую и цифровую схемы полевых МОП-транзисторов в одной интегральной схеме со смешанными сигналами , что делает необходимое пространство на плате еще меньше. Это создает необходимость изолировать аналоговые схемы от цифровых на уровне микросхемы, что приводит к использованию изоляционных колец и кремния на изоляторе (SOI). Поскольку MOSFET требует больше места для обработки заданного количества энергии, чем BJT, процессы изготовления могут включать BJT и MOSFET в одно устройство. Устройства со смешанными транзисторами называются bi-FET (биполярными полевыми транзисторами), если они содержат только один BJT-FET, и BiCMOS (биполярно-CMOS), если они содержат дополнительные BJT-FET. Такие устройства имеют преимущества как изолированных вентилей, так и более высокой плотности тока.

В конце 1980-х Асад Абиди первым изобрел технологию RF CMOS , которая использует схемы MOS VLSI , работая в UCLA . Это изменило способ проектирования ВЧ-схем , от дискретных биполярных транзисторов к интегральным схемам КМОП. С 2008 года радиоприемопередатчики во всех беспроводных сетевых устройствах и современных мобильных телефонах массово производятся как устройства RF CMOS. RF CMOS также используется почти во всех современных устройствах Bluetooth и беспроводной локальной сети (WLAN). [160]

MOS-память [ править ]

Появление полевого МОП-транзистора позволило на практике использовать МОП-транзисторы в качестве элементов хранения ячеек памяти - функцию, ранее выполняемую магнитными сердечниками в компьютерной памяти . [161] Первая современная компьютерная память была представлена в 1965 году, когда Джон Шмидт из Fairchild Semiconductor разработал первую полупроводниковую МОП- память , 64-битную МОП- память (статическая память с произвольным доступом ). [162] SRAM стала альтернативой памяти с магнитным сердечником , но для каждого бита данных требовалось шесть МОП-транзисторов . [163]

Технология MOS является основой DRAM (динамической памяти с произвольным доступом ). В 1966 году доктор Роберт Х. Деннард из исследовательского центра IBM Thomas J. Watson работал над MOS-памятью . Изучая характеристики технологии МОП, он обнаружил, что она способна создавать конденсаторы , и что сохранение заряда или отсутствие заряда на МОП-конденсаторе может представлять 1 и 0 бита, в то время как МОП-транзистор может управлять записью заряда в конденсатор. Это привело к его разработке ячейки памяти DRAM с одним транзистором. [163]В 1967 году Деннард подал в IBM патент на ячейку памяти DRAM с одним транзистором (динамическая память с произвольным доступом), основанная на технологии MOS. [164] MOS-память обеспечивала более высокую производительность, была дешевле и потребляла меньше энергии, чем память с магнитным сердечником , что привело к тому, что MOS-память обогнала память с магнитным сердечником в качестве доминирующей технологии компьютерной памяти к началу 1970-х годов. [165]

Фрэнк Ванласс , изучая структуры MOSFET в 1963 году, заметил движение заряда через оксид на затвор . Хотя он этого и не добился, эта идея позже стала основой для технологии EPROM (стираемая программируемая постоянная память ). [166] В 1967 году Давон Кан и Саймон Мин Сзе предложили использовать ячейки памяти с плавающим затвором , состоящие из полевых МОП-транзисторов с плавающим затвором (FGMOS), для создания перепрограммируемого ПЗУ ( постоянное запоминающее устройство ). [167] Ячейки памяти с плавающей запятой позже стали основой дляТехнологии энергонезависимой памяти (NVM), включая EPROM, EEPROM (электрически стираемое программируемое ПЗУ) и флэш-память . [168]

Бытовая электроника [ править ]

МОП-транзисторы широко используются в бытовой электронике . Один из самых ранних влиятельных потребительских электронных продуктов с поддержкой схемами MOS БИС был электронный карманный калькулятор , [154] , как технология MOS LSI позволила большое количество вычислительных возможностей в небольших упаковках. [169] В 1965 году настольный калькулятор Victor 3900 был первым МОП- калькулятором с 29 МОП-микросхемами. [170] В 1967 году Texas Instruments Cal-Tech был первым прототипом портативного электронного калькулятора с тремя микросхемами MOS LSI, а позже был выпущен как Canon.Pocketronic в 1970 году [171] Sharp QT-8D настольный калькулятор был первым массового производства БИС МОП - калькулятор в 1969 году, [172] и Sharp EL-8 , которые используются четыре МОП LSI чипов был первым коммерческим электронным ручной калькулятор в 1970 году . [171] Первым настоящим карманным калькулятором был Busicom LE-120A HANDY LE, в котором использовался единственный калькулятор MOS LSI на кристалле от Mostek , и он был выпущен в 1971 году. [171] К 1972 году схемы MOS LSI были коммерциализированы для множества других приложений. [173]

MOSFETs имеет основополагающее значение для информационных и коммуникационных технологий (ИКТ), [66] [79] в том числе современных компьютеров , [174] [146] [155] современные вычисления , [175] телекоммуникация , то инфраструктура связи , [174] [176] в Интернет , [174] [72] [177] цифровая телефония , [178] беспроводная связь, [179] [180] и мобильные сети . [180]По словам Колинджа, современная компьютерная промышленность и цифровые телекоммуникационные системы не существовали бы без полевого МОП-транзистора. [146] Достижения в технологии MOS явились наиболее важным фактором быстрого роста пропускной способности сети в телекоммуникационных сетях , при этом пропускная способность удваивается каждые 18 месяцев, с бит в секунду до терабит в секунду ( закон Эдхольма ). [181]

Датчики MOS [ править ]

Датчики MOS , также известные как датчики MOSFET, широко используются для измерения физических , химических , биологических параметров и параметров окружающей среды . [130] ион-чувствительный полевой транзистор (ИСПТ), например, широко используется в биомедицинских применений. [132] МОП- хеморезисторы и полевые МОП-транзисторы также были широко продемонстрированы как многообещающие области применения для измерения газа либо в качестве отдельных сенсорных устройств, либо в качестве компонентов в массивах химических сенсоров . [182]

МОП-транзисторы также широко используются в микроэлектромеханических системах (МЭМС), поскольку кремниевые МОП-транзисторы могут взаимодействовать и взаимодействовать с окружающей средой и обрабатывать такие вещи, как химические вещества , движения и свет . [183] Ранним примером устройства MEMS является транзистор с резонансным затвором, адаптация полевого МОП-транзистора, разработанный Харви К. Натансоном в 1965 году. [184]

Технология MOS является основой для современных датчиков изображения , включая устройство с зарядовой связью (CCD) и датчик CMOS с активными пикселями (CMOS-датчик), используемых в цифровых изображениях и цифровых камерах . [77] Уиллард Бойл и Джордж Э. Смит разработали ПЗС-матрицу в 1969 году. Изучая процесс МОП, они поняли, что электрический заряд аналогичен магнитному пузырю и что он может храниться на крошечном МОП-конденсаторе. Поскольку было довольно просто изготовить серию МОП-конденсаторов в ряд, они подключали к ним подходящее напряжение, чтобы заряд мог переходить от одного к другому. [77]ПЗС - это полупроводниковая схема, которая позже использовалась в первых цифровых видеокамерах для телевещания . [185]

MOS датчик активного пикселя (APS) был разработан Цутому Накамура на Олимпе в 1985 году [186] CMOS датчик активный пиксель был впоследствии разработан Эриком Фоссум и его команда в НАСА «s Лаборатории реактивного движения в начале 1990 - х годов. [187]

Датчики изображения MOS широко используются в технологии оптических мышей . В первой оптической мыши, изобретенной Ричардом Ф. Лайоном в Xerox в 1980 году, использовался сенсорный чип NMOS 5 мкм . [188] [189] С момента появления первой коммерческой оптической мыши IntelliMouse, представленной в 1999 году, в большинстве оптических мышей используются датчики CMOS. [190]

Силовые МОП-транзисторы [ править ]

MOSFET власти является наиболее широко используемым устройством питания в мире. [4] Преимущества перед транзисторами с биполярным переходом в силовой электронике включают полевые МОП-транзисторы, не требующие непрерывного потока управляющего тока, чтобы оставаться во включенном состоянии, предлагающие более высокие скорости переключения, более низкие потери мощности переключения, более низкое сопротивление в открытом состоянии и пониженную подверженность тепловому разгоне. [191] Силовой полевой МОП-транзистор повлиял на источники питания , позволив повысить рабочие частоты, уменьшить размер и вес, а также увеличить объемы производства. [192]

Импульсные источники питания - наиболее распространенное применение для силовых полевых МОП-транзисторов. [53] Они также широко используются для MOS усилителей мощности RF , которые позволили осуществить переход мобильных сетей с аналоговых на цифровые в 1990-х годах. Это привело к широкому распространению беспроводных мобильных сетей, которые произвели революцию в системах электросвязи . [179] LDMOS , в частности , является наиболее широко используется усилитель мощности в мобильных сетях, таких как 2G , 3G , [179] 4G и 5G . [180] Более 50 миллиардов полевых МОП-транзисторов с дискретной мощностью отгружается ежегодно, по состоянию на 2018 год. Они широко используются , в частности, в автомобильных , промышленных и коммуникационных системах . [193] Силовые МОП-транзисторы обычно используются в автомобильной электронике , в частности, в качестве переключающих устройств в электронных блоках управления , [194] и в качестве преобразователей энергии в современных электромобилях . [195] биполярный транзистор с изолированным затвором (IGBT), гибрид МОП-биполярный транзистор, также используется для самых разнообразных применений. [196]

Строительство [ править ]

Материал ворот [ править ]

Основным критерием выбора материала затвора является его хорошая проводимость . Сильнолегированный поликристаллический кремний является приемлемым, но определенно не идеальным проводником, а также страдает некоторыми дополнительными техническими недостатками в своей роли стандартного материала затвора. Тем не менее, есть несколько причин в пользу использования поликремния:

- Пороговое напряжение (и , следовательно , утечка к источнику тока на) модифицируются функция работы разницы между затвором материалом и материалом канала. Поскольку поликремний является полупроводником, его работу выхода можно модулировать, регулируя тип и уровень легирования. Кроме того, поскольку поликремний имеет ту же запрещенную зону, что и нижележащий кремниевый канал, довольно просто настроить работу выхода для достижения низких пороговых напряжений как для устройств NMOS, так и для устройств PMOS. Напротив, работу выхода металлов нелегко модулировать, поэтому настройка работы выхода для получения низких пороговых напряжений(LVT) становится серьезной проблемой. Кроме того, получение низкопороговых устройств на устройствах PMOS и NMOS иногда требует использования разных металлов для каждого типа устройства. Хотя биметаллические интегральные схемы (т. Е. Один тип металла для электродов затвора NFETS и второй тип металла для электродов затвора PFETS) не распространены, они известны в патентной литературе и обеспечивают некоторые преимущества с точки зрения настройки электрических схем в целом. электрические характеристики.

- Граница раздела кремний-SiO 2 хорошо изучена и, как известно, имеет относительно небольшое количество дефектов. Напротив, многие интерфейсы металл-изолятор содержат значительные уровни дефектов, которые могут привести к закреплению уровня Ферми , зарядке или другим явлениям, которые в конечном итоге ухудшают характеристики устройства.

- В процессе изготовления ИС полевого МОП-транзистора предпочтительно наносить материал затвора перед определенными высокотемпературными этапами, чтобы сделать транзисторы с лучшими характеристиками. Такие высокотемпературные этапы плавили бы некоторые металлы, ограничивая типы металлов, которые могут использоваться в процессе на основе металлических затворов.

Хотя ворота из поликремния были стандартом де-факто в течение последних двадцати лет, у них действительно есть некоторые недостатки, которые привели к их вероятной замене в будущем металлическими воротами. К этим недостаткам можно отнести:

- Поликремний не является хорошим проводником (примерно в 1000 раз более резистивным, чем металлы), что снижает скорость распространения сигнала через материал. Удельное сопротивление можно снизить, увеличив уровень легирования, но даже сильно легированный поликремний не так проводит, как большинство металлов. Для дальнейшего улучшения проводимости иногда высокотемпературный металл, такой как вольфрам , титан , кобальт , а в последнее время никель , легируют верхними слоями поликремния. Такой смешанный материал называется силицид.. Комбинация силицида и поликремния имеет лучшие электрические свойства, чем один поликремний, и все же не плавится при последующей обработке. Кроме того, пороговое напряжение не намного выше, чем у одного поликремния, потому что силицидный материал не находится рядом с каналом. Процесс, в котором силицид образуется как на электроде затвора, так и в областях истока и стока, иногда называют салицидом , самовыравнивающимся силицидом.

- Когда транзисторы сильно уменьшены в масштабе, необходимо сделать диэлектрический слой затвора очень тонким, около 1 нм в современных технологиях. Наблюдаемое здесь явление представляет собой так называемое поликристаллическое обеднение , когда обедненный слой образуется в слое поликремния затвора рядом с диэлектриком затвора, когда транзистор находится в инверсии. Чтобы избежать этой проблемы, желательна металлическая калитка. Разнообразные металлические ворота , такие как тантал , вольфрам, нитрид тантала и нитрида титана используют, как правило , в сочетании с высокой каппа диэлектриков . Альтернативой является использование затворов из полностью кремниевого поликремния, процесс, известный как FUSI.