Эта статья требует дополнительных ссылок для проверки . ( июль 2010 г. ) ( Узнайте, как и когда удалить этот шаблон сообщения ) |

| Память компьютера и типы хранилищ данных |

|---|

| Общий |

|

| Летучий |

| баран |

|

| Исторический |

|

| Энергонезависимая |

| ПЗУ |

|

| NVRAM |

|

| Ранняя стадия NVRAM |

|

| Аналоговая запись |

|

| Оптический |

|

| В развитии |

|

| Исторический |

|

Статическая память с произвольным доступом ( статическая RAM или SRAM ) - это тип памяти с произвольным доступом (RAM), в которой для хранения каждого бита используется схема фиксации (триггер) . SRAM - это энергозависимая память ; данные теряются при отключении питания.

Термин статический отличает SRAM от DRAM ( динамической памяти с произвольным доступом), которую необходимо периодически обновлять . SRAM быстрее и дороже, чем DRAM; он обычно используется для кэш - памяти и внутренних регистров одного процессора в то время как DRAM , используется для компьютера основной памяти .

История [ править ]

Полупроводниковый биполярный SRAM был изобретен в 1963 году Робертом Норманом в Fairchild Semiconductor. [1] МОП SRAM была изобретена в 1964 году Джоном Шмидтом в Fairchild Semiconductor. Это была 64-битная MOS p-канальная SRAM. [2] [3]

В 1965 году [4] Арнольд Фарбер и Юджин Шлиг, работающие в IBM, создали ячейку памяти с жестким подключением , используя затвор транзистора и защелку туннельного диода . Они заменили защелку двумя транзисторами и двумя резисторами , конфигурация, которая стала известна как ячейка Фарбера-Шлига. В 1965 году Бенджамин Агуста и его команда в IBM создали 16-битный кремниевый чип памяти на основе ячейки Фарбера-Шлига с 80 транзисторами, 64 резисторами и 4 диодами.

Приложения и использование [ править ]

Характеристики [ править ]

Хотя его можно охарактеризовать как энергозависимую память, SRAM демонстрирует постоянство данных . [5]

SRAM предлагает простую модель доступа к данным и не требует схемы обновления. Производительность и надежность хорошие, а энергопотребление в режиме ожидания низкое.

Из-за количества транзисторов, необходимых для реализации ячейки SRAM, плотность уменьшается, а цена увеличивается по сравнению с DRAM, а потребление энергии велико, когда данные активно считываются или записываются.

Тактовая частота и мощность [ править ]

Мощность потребления SRAM колеблется в широких пределах в зависимости от того, как часто к ней обращаются. Было предложено несколько методов управления энергопотреблением структур памяти на основе SRAM. [6]

Встроенное использование [ править ]

Многие категории промышленных и научных подсистем, автомобильной электроники и т. Д. Содержат статическое ОЗУ, которое в этом контексте может называться ESRAM . [7] Некоторое количество (килобайты или меньше) также встроено практически во все современные устройства, игрушки и т. Д., Которые реализуют электронный пользовательский интерфейс. Несколько мегабайт можно использовать в сложных продуктах, таких как цифровые фотоаппараты, сотовые телефоны, синтезаторы, игровые приставки и т. Д.

SRAM в его двухпортовой форме иногда используется для схем цифровой обработки сигналов в реальном времени . [8]

В компьютерах [ править ]

SRAM также используется в персональных компьютерах, рабочих станциях, маршрутизаторах и периферийном оборудовании: файлы регистров ЦП , внутренние кэши ЦП и внешние кеши SRAM в пакетном режиме , буферы жесткого диска, буферы маршрутизатора и т. Д. ЖК-экраны и принтеры также обычно используют статическое ОЗУ для хранения изображение отображается (или должно быть распечатано). Статическая RAM использовалась для основной памяти большинства ранних персональных компьютеров, таких как ZX80 , TRS-80 Model 100 и Commodore VIC-20 .

Любители [ править ]

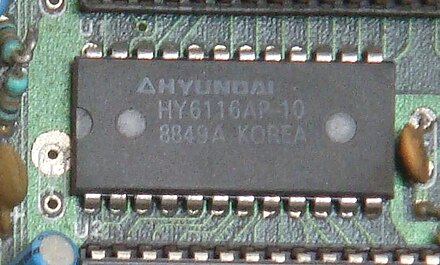

Любители, особенно энтузиасты самодельных процессоров, [9] часто предпочитают SRAM из-за простоты взаимодействия. С ней намного проще работать, чем с DRAM, поскольку здесь нет циклов обновления, а шины адреса и данных часто доступны напрямую. [ необходима цитата ] В дополнение к шинам и соединениям питания для SRAM обычно требуется только три элемента управления: Chip Enable (CE), Write Enable (WE) и Output Enable (OE). В синхронной SRAM также включены часы (CLK). [ необходима цитата ]

Типы SRAM [ править ]

Энергонезависимая SRAM [ править ]

Энергонезависимая SRAM (nvSRAM) имеет стандартные функции SRAM, но они сохраняют данные при отключении питания, обеспечивая сохранение важной информации. nvSRAM используются в широком диапазоне ситуаций - сетевых, аэрокосмических и медицинских, среди многих других [10] - где сохранение данных имеет решающее значение, а батареи нецелесообразны.

Псевдо SRAM [ править ]

Псевдостатическая RAM (PSRAM) имеет ядро памяти DRAM в сочетании со схемой самообновления. [11] Внешне они выглядят как более медленная SRAM. У них есть преимущество плотности / стоимости по сравнению с истинным SRAM, без сложности доступа к DRAM.

По типу транзистора [ править ]

- Биполярный переходной транзистор (используется в TTL и ECL ) - очень быстрый, но с высоким энергопотреблением

- MOSFET (используется в CMOS ) - маломощный и очень распространенный сегодня

По типу триггера [ править ]

- Двоичная SRAM

- Тернарная SRAM

По функции [ править ]

- Асинхронный - не зависит от тактовой частоты; ввод и вывод данных контролируются переходом адреса. Примеры включают в себя широко распространенные 28-контактные микросхемы 8K × 8 и 32K × 8 (часто, но не всегда называемые чем-то вроде 6264 и 62C256 соответственно), а также аналогичные продукты до 16 Мбит на чип.

- Синхронный - все тайминги инициируются фронтом (ами) часов. Адрес, входные данные и другие управляющие сигналы связаны с тактовыми сигналами.

В 1990-х годах асинхронная SRAM использовалась для быстрого доступа. Асинхронная SRAM использовалась в качестве основной памяти для небольших встроенных процессоров без кеша, используемых во всем, от промышленной электроники и измерительных систем до жестких дисков и сетевого оборудования, а также во многих других приложениях. В настоящее время синхронная SRAM (например, DDR SRAM) используется скорее аналогично синхронной DRAM - используется память DDR SDRAM, а не асинхронная DRAM. Интерфейс синхронной памяти намного быстрее, поскольку время доступа может быть значительно сокращено за счет использования конвейера.архитектура. Кроме того, поскольку DRAM намного дешевле, чем SRAM, SRAM часто заменяется DRAM, особенно в случае, когда требуется большой объем данных. Однако память SRAM намного быстрее для произвольного (не блочного / пакетного) доступа. Следовательно, память SRAM в основном используется для кеш-памяти ЦП , небольшой встроенной памяти, FIFO или других небольших буферов.

По функции [ править ]

- Zero bus turnaround (ZBT) - оборот - это количество тактов, необходимое для изменения доступа к SRAM с записи на чтение и наоборот. Оборот для ZBT SRAM или задержка между циклом чтения и записи равна нулю.

- syncBurst (syncBurst SRAM или синхронно-пакетная SRAM) - обеспечивает синхронный пакетный доступ к записи в SRAM для увеличения операций записи в SRAM

- DDR SRAM - синхронный, один порт чтения / записи, удвоенная скорость ввода / вывода

- SRAM с четырехкратной скоростью передачи данных - синхронный, отдельные порты чтения и записи, четырехкратная скорость ввода-вывода

Интегрирован в чип [ править ]

SRAM может быть интегрирована в качестве ОЗУ или кэш-памяти в микроконтроллеры (обычно от 32 до 128 килобайт ), в качестве основных кешей в мощных микропроцессорах, таких как семейство x86 и многих других (от 8 КБ до многих мегабайт), для хранения регистров и частей конечных автоматов, используемых в некоторых микропроцессорах (см. файл регистров ), на специализированных ИС или ASIC (обычно в килобайтах), а также в программируемой логической матрице и сложной программируемой логике. Устройство

Дизайн [ править ]

Типичная ячейка SRAM состоит из шести полевых МОП-транзисторов . Каждый бит в SRAM хранится на четырех транзисторах (M1, M2, M3, M4), которые образуют два инвертора с перекрестной связью. Эта ячейка памяти имеет два стабильных состояния, которые используются для обозначения 0 и 1 . Два дополнительных транзистора доступа служат для управления доступом к ячейке памяти во время операций чтения и записи. В дополнение к такой шеститранзисторной (6T) SRAM, другие типы микросхем SRAM используют 4, 8, 10 (4T, 8T, 10T SRAM) или более транзисторов на бит. [12] [13] [14]Четырехтранзисторная SRAM довольно распространена в автономных устройствах SRAM (в отличие от SRAM, используемой для кэшей ЦП), реализована в специальных процессах с дополнительным слоем поликремния , что позволяет использовать подтягивающие резисторы с очень высоким сопротивлением. [15] Принципиальным недостатком использования 4T SRAM является повышенная статическая мощность из-за постоянного тока, протекающего через один из понижающих транзисторов.

Иногда это используется для реализации более одного порта (для чтения и / или записи), что может быть полезно в определенных типах видеопамяти и файлов регистров, реализованных с помощью многопортовой схемы SRAM.

Как правило, чем меньше транзисторов требуется на ячейку, тем меньше может быть каждая ячейка. Поскольку стоимость обработки кремниевой пластины относительно фиксирована, использование ячеек меньшего размера и, таким образом, размещение большего количества битов на одной пластине снижает стоимость одного бита памяти.

Возможны ячейки памяти, в которых используется менее четырех транзисторов, но такие ячейки 3T [16] [17] или 1T являются DRAM, а не SRAM (даже так называемой 1T-SRAM ).

Доступ к ячейке обеспечивается словарной линией (WL на рисунке), которая управляет двумя транзисторами доступа M 5 и M 6, которые, в свою очередь, определяют, должна ли ячейка быть подключена к битовым линиям: BL и BL. Они используются для передачи данных как для операций чтения, так и для записи. Хотя не обязательно иметь две битовые линии, как сигнал, так и его инверсия обычно предоставляются для улучшения запаса по шуму .

Во время доступа для чтения битовые линии активно управляются высоким и низким уровнями инверторов в ячейке SRAM. Это улучшает полосу пропускания SRAM по сравнению с DRAM - в DRAM битовая линия подключена к накопительным конденсаторам, а разделение заряда заставляет битовую линию качаться вверх или вниз. Симметричная структура SRAM также позволяет использовать дифференциальную сигнализацию , что упрощает обнаружение небольших колебаний напряжения. Еще одно отличие DRAM, которое способствует ускорению SRAM, заключается в том, что коммерческие микросхемы принимают все биты адреса одновременно. Для сравнения, обычные DRAM имеют адрес, мультиплексированный на две половины, то есть старшие биты, за которыми следуют младшие биты, по тем же выводам корпуса, чтобы уменьшить их размер и стоимость.

Размер SRAM с m адресными строками и n строками данных составляет 2 m слов или 2 m × n бит. Чаще всего размер слова составляет 8 бит, что означает, что один байт может быть прочитан или записан в каждое из 2 м различных слов в микросхеме SRAM. Несколько общих микросхем SRAM имеют 11 адресных линий (таким образом, емкость 2 11 = 2048 = 2 k слов) и 8-битное слово, поэтому они называются «2k × 8 SRAM».

Размеры ячейки SRAM на ИС определяются минимальным размером элемента процесса, используемого для создания ИС.

Операция SRAM [ править ]

Ячейка SRAM имеет три различных состояния: резервное (цепь простаивает), чтение (данные запрошены) или запись (обновление содержимого). SRAM, работающая в режиме чтения и записи, должна иметь «читаемость» и «стабильность записи» соответственно. Три разных состояния работают следующим образом:

Ожидание [ править ]

Если словарная шина не установлена, транзисторы доступа M 5 и M 6 отключают ячейку от битовых линий. Два перекрестно связанных инвертора, образованные M 1 - M 4, будут продолжать усиливать друг друга, пока они подключены к источнику питания.

Чтение [ править ]

Теоретически для чтения требуется только подтверждение словарной шины WL и считывание состояния ячейки SRAM с помощью одного транзистора доступа и разрядной шины, например M 6 , BL. Однако разрядные линии относительно длинные и имеют большую паразитную емкость . Для ускорения чтения на практике используется более сложный процесс: цикл чтения начинается с предварительной зарядки обеих битовых линий BL и BL до высокого (логическая 1 ) напряжения. Затем утверждение словарной шины WL включает оба транзистора доступа M 5 и M 6 , что вызывает небольшое падение напряжения одной разрядной шины BL. Тогда BL и BLлинии будут иметь небольшую разницу в напряжении между ними. Усилитель считывания определит, какая линия имеет более высокое напряжение, и, таким образом, определит, было ли сохранено 1 или 0 . Чем выше чувствительность усилителя считывания, тем быстрее выполняется считывание. Чем мощнее NMOS, тем легче выполнить раскрытие. Поэтому разрядные шины традиционно предварительно заряжаются до высокого напряжения. Многие исследователи также пытаются произвести предварительную зарядку при немного более низком напряжении, чтобы снизить энергопотребление. [18] [19]

Написание [ править ]

Цикл записи начинается с применения записываемого значения к битовым строкам. Если мы хотим записать 0 , мы бы применили 0 к битовым строкам, то есть установили BL в 1 и BL в 0 . Это похоже на применение импульса сброса к SR-защелке , который заставляет триггер менять состояние. 1 записывается путем инвертирования значений битовых строк. Затем утверждается WL, и значение, которое должно быть сохранено, фиксируется. Это работает, потому что драйверы ввода битовой линии разработаны так, чтобы быть намного сильнее, чем относительно слабые транзисторы в самой ячейке, поэтому они могут легко переопределить предыдущее состояние кросс-связанные инверторы. На практике доступ к NMOS-транзисторам M5 и M 6 должны быть сильнее, чем нижние NMOS (M 1 , M 3 ) или верхние PMOS (M 2 , M 4 ) транзисторы. Это легко получить, поскольку транзисторы PMOS намного слабее, чем NMOS, при том же размере. Следовательно, когда одна пара транзисторов (например, M 3 и M 4 ) лишь слегка отменяется процессом записи, напряжение затвора противоположной пары транзисторов (M 1 и M 2 ) также изменяется. Это означает, что транзисторы M 1 и M 2 легче переопределить и так далее. Таким образом, инверторы с перекрестной связью увеличивают процесс записи.

Поведение автобуса [ править ]

ОЗУ со временем доступа 70 нс будет выводить действительные данные в течение 70 нс с момента, когда адресные строки действительны. Некоторые SRAM имеют "страничный режим", в котором слова страницы (256, 512 или 1024 слова) могут быть прочитаны последовательно со значительно более коротким временем доступа (обычно приблизительно 30 нс). Страница выбирается путем установки верхних адресных строк, а затем слова последовательно считываются путем пошагового перехода по нижним адресным строкам.

См. Также [ править ]

- Флэш-память

- Миниатюрная карта , снятый с производства стандарт карт памяти SRAM

Ссылки [ править ]

- ^ «1966: Полупроводниковые ОЗУ служат для высокоскоростных запоминающих устройств» . Музей истории компьютеров . Проверено 19 июня 2019 .

- ^ "1970: MOS динамическая RAM конкурирует с памятью на магнитных сердечниках по цене" .

- ^ "Лекции памяти" (PDF) .

- ^ "Неразрушающий массив памяти" .

- ↑ Сергей Скоробогатов (июнь 2002 г.). «Низкая остаточная информация Температуры в статической оперативной памяти» . Кембриджский университет, компьютерная лаборатория . Проверено 27 февраля 2008 . Цитировать журнал требует

|journal=( помощь ) - ^ « Обзор архитектурных методов для повышения энергоэффективности кэша », С. Миттал, SUSCOM, 4 (1), 33–43, 2014

- ↑ Фахад Ариф (5 апреля 2014 г.). «Microsoft заявляет, что ESRAM для Xbox One - это« огромная победа »- объясняет, как она позволяет достичь 1080p / 60 FPS» . Проверено 24 марта 2020 .

- ^ Интерфейс общей памяти с TMS320C54x DSP (PDF) , получено 4 мая 2019 г.

- ^ "Самодельный процессор" .

- ^ Компьютерная организация (4-е изд.). [Sl]: Макгроу-Хилл. 1996-07-01. ISBN 978-0-07-114323-3.

- ^ "3.0V Core Async / Page PSRAM Memory" (PDF) . Микрон . Проверено 4 мая 2019 .

- ^ Kulkarni, Jaydeep P .; Ким, Киджонг; Рой, Кошик (2007). «Надежная подпороговая SRAM на основе триггера Шмитта на 160 мВ». Журнал IEEE по твердотельным схемам . 42 (10): 2303. Bibcode : 2007IJSSC..42.2303K . DOI : 10.1109 / JSSC.2007.897148 . S2CID 699469 .

- ^ Патент США 6975532: Квазистатическая память с произвольным доступом

- ^ «Оптимизация площади в ячейках SRAM 6T и 8T с учетом V-го изменения в будущих процессах - MORITA и др. E90-C (10): 1949 - Сделки IEICE по электронике» . Архивировано из оригинала на 2008-12-05.

- ^ Престон, Рональд П. (2001). «14: Регистрация файлов и кешей» (PDF) . Проектирование высокопроизводительных микропроцессорных схем . IEEE Press. п. 290.

- ^ Патент США 6975531: 3-транзисторная ячейка усиления DRAM 6F2

- ^ Технология 3T-iRAM (r)

- ^ Система предварительной зарядки SRAM для снижения мощности записи

- ^ Правила проектирования с высокой скоростью и низким энергопотреблением для предварительной зарядки и самосинхронизации SRAM при технологических вариациях